# **MCP2517FD**

# **External CAN FD Controller with SPI Interface**

# Features

### <u>General</u>

- External CAN FD Controller with SPI Interface

- · Arbitration Bit Rate up to 1 Mbps

- · Data Bit Rate up to 8 Mbps

- · CAN FD Controller modes

- Mixed CAN 2.0B and CAN FD mode

CAN 2.0B mode

- Conforms to ISO11898-1:2015

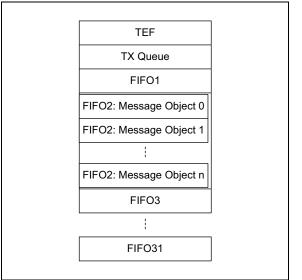

#### Message FIFOs

- 31 FIFOs, configurable as transmit or receive FIFOs

- One Transmit Queue (TXQ)

- · Transmit Event FIFO (TEF) with 32 bit time stamp

#### Message Transmission

- Message transmission prioritization:

- Based on priority bit field, and/or

- Message with lowest ID gets transmitted first using the Transmit Queue (TXQ)

- Programmable automatic retransmission attempts: unlimited, 3 attempts or disabled

#### Message Reception

- · 32 Flexible Filter and Mask Objects

- · Each object can be configured to filter either:

- Standard ID + first 18 data bits, or

- Extended ID

- 32-bit Time Stamp

#### **Special Features**

- VDD: 2.7 to 5.5V

- Active current: max. 12 mA @5.5 V, 40 MHz CAN clock

- Sleep current: 10 µA, typical

- · Message objects are located in RAM: 2 KB

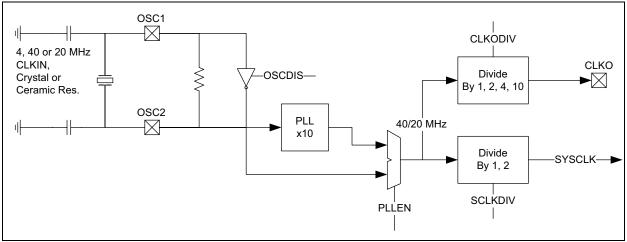

- Up to 3 configurable interrupt pins

- Bus Health Diagnostics and Error counters

- Transceiver standby control

- Start of frame pin for indicating the beginning of messages on the bus

- · Temperature ranges:

- High (H): -40°C to +150°C

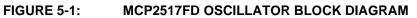

#### **Oscillator Options**

- 40, 20 or 4 MHz crystal, or ceramic resonator; or external clock input

- Clock output with prescaler

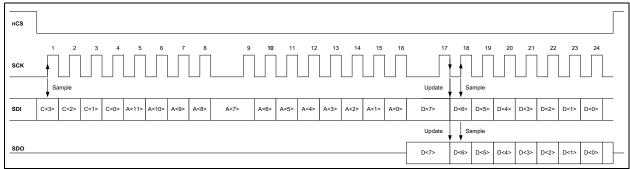

#### **SPI Interface**

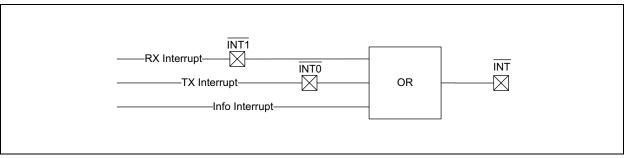

- Up to 20 MHz SPI clock speed

- Supports SPI modes 0,0 and 1,1

- Registers and bit fields are arranged in a way to enable efficient access via SPI

### Safety Critical Systems

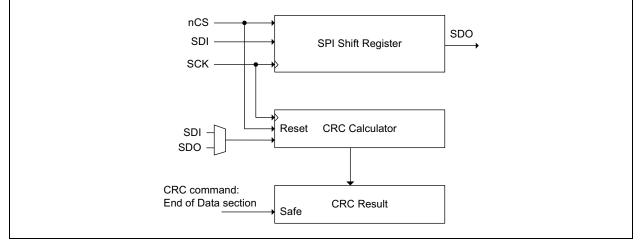

- SPI commands with CRC to detect noise on SPI interface

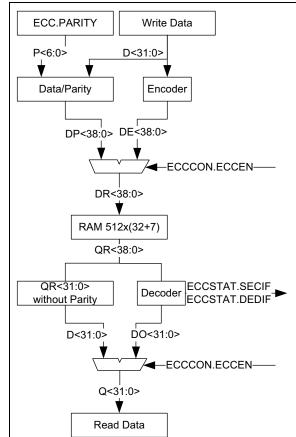

- Error Correction Code (ECC) protected RAM

#### Additional Features

- GPIO pins: INT0 and INT1 can be configured as general purpose I/O

- Open drain outputs: TXCAN, INT, INTO, and INT1 pins can be configured as push/pull or open drain outputs

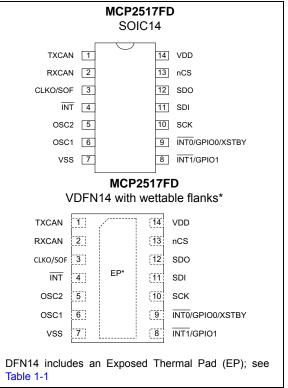

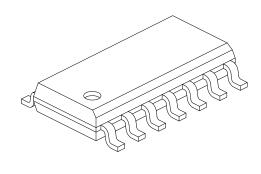

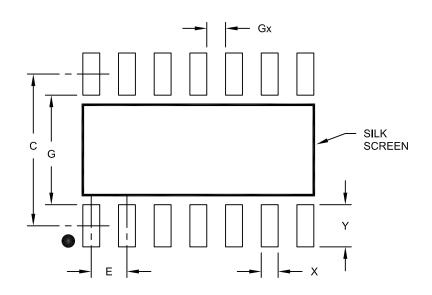

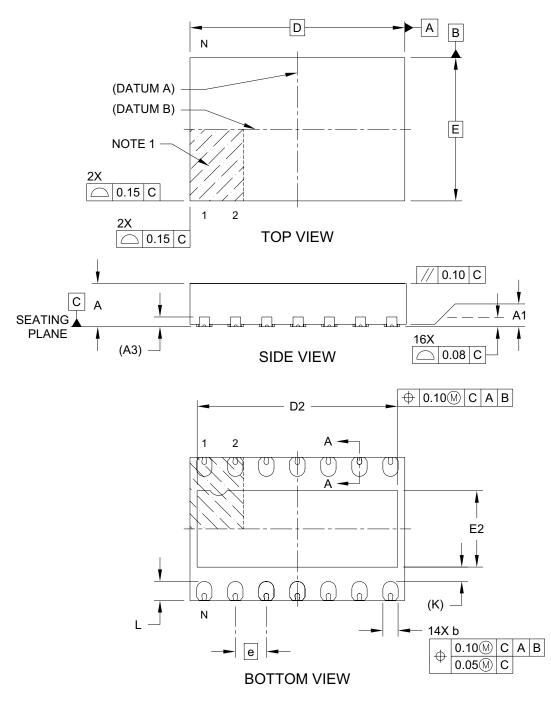

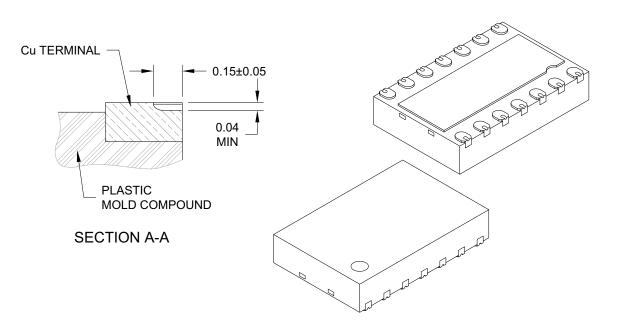

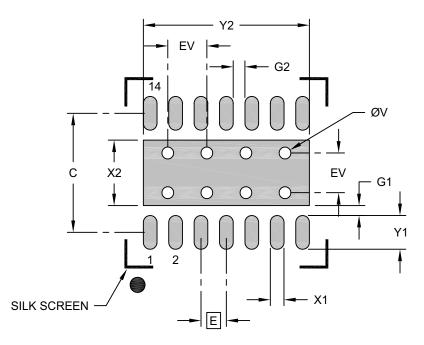

# Package Types

# 1.0 DEVICE OVERVIEW

The MCP2517FD is a cost-effective and small-footprint CAN FD controller that can be easily added to a microcontroller with an available SPI interface. Therefore, a CAN FD channel can be easily added to a microcontroller that is either lacking a CAN FD peripheral, or that doesn't have enough CAN FD channels.

The MCP2517FD supports both, CAN frames in the Classical format (CAN2.0B) and CAN Flexible Data Rate (CAN FD) format, as specified in ISO11898-1:2015.

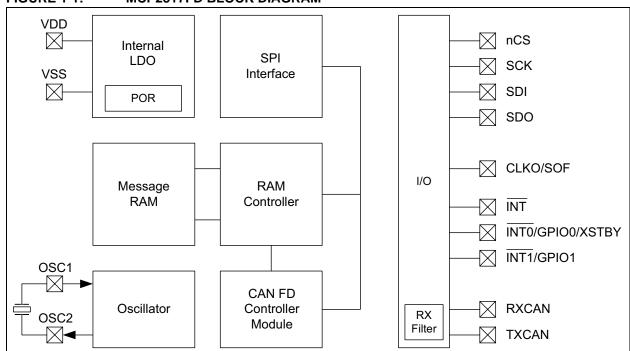

# 1.1 Block Diagram

Figure 1.1 shows the block diagram of the MCP2517FD. The MCP2517FD contains the following main blocks:

- The CAN FD Controller module implements the CAN FD protocol and contains the FIFOs, and Filters.

- The SPI interface is used to control the device by accessing SFRs and RAM.

- The RAM controller arbitrates the RAM accesses between the SPI and CAN FD Controller module.

- The Message RAM is used to store the data of the Message Objects.

- · The oscillator generates the CAN clock.

- The Internal LDO and POR circuit.

- The I/O control.

Note 1: This data sheet summarizes the features of the MCP2517FD. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP2517FD Family Reference Manual".

#### FIGURE 1-1: MCP2517FD BLOCK DIAGRAM

# 1.2 Pin Out Description

Table 1-1 describes the functions of the pins.

| TABLE 1-1: | MCP2517FD STANDARD PINOUT VERSION |

|------------|-----------------------------------|

|            |                                   |

| Pin Name                              | SOIC           | VDFN        | Pin Type | Description                                                          |  |  |  |

|---------------------------------------|----------------|-------------|----------|----------------------------------------------------------------------|--|--|--|

| TXCAN                                 | 1              | 1           | 0        | Transmit output to CAN FD transceiver                                |  |  |  |

| RXCAN                                 | 2              | 2           | I        | Receive input from CAN FD transceiver                                |  |  |  |

| CLKO/SOF                              | 3              | 3           | 0        | Clock output/Start of Frame output                                   |  |  |  |

| INT                                   | 4              | 4           | 0        | Interrupt output (active low)                                        |  |  |  |

| OSC2                                  | 5              | 5           | 0        | External oscillator output                                           |  |  |  |

| OSC1                                  | 6              | 6           | I        | External oscillator input                                            |  |  |  |

| VSS                                   | 7              | 7           | Р        | Ground                                                               |  |  |  |

| INT1/GPIO1                            | 8              | 8           | I/O      | RX Interrupt output (active low)/GPIO                                |  |  |  |

| INT0/GPIO0/<br>XSTBY                  | 9              | 9           | I/O      | TX Interrupt output (active low)/GPIO/<br>Transceiver Standby output |  |  |  |

| SCK                                   | 10             | 10          | I        | SPI clock input                                                      |  |  |  |

| SDI                                   | 11             | 11          | I        | SPI data input                                                       |  |  |  |

| SDO                                   | 12             | 12          | 0        | SPI data output                                                      |  |  |  |

| nCS                                   | 13             | 13          | I        | SPI chip select input                                                |  |  |  |

| VDD                                   | 14             | 14          | Р        | Positive Supply                                                      |  |  |  |

| EP - 15 P Exposed Pad; connect to VSS |                |             |          |                                                                      |  |  |  |

| Legend: P =                           | Power, I = Inp | ut, O = Out | put      |                                                                      |  |  |  |

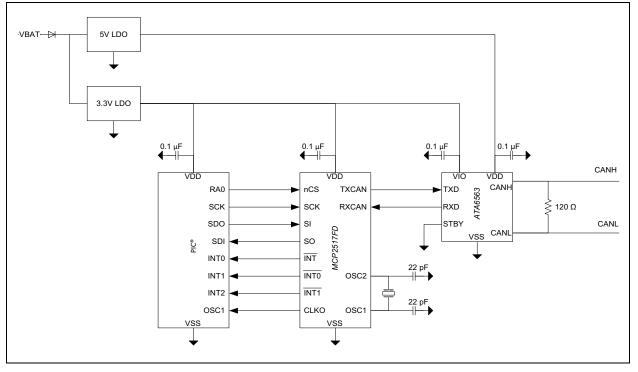

# **1.3** Typical Application

Figure 1-2 shows an example of a typical application of the MCP2517FD. In this example, the microcontroller operates at 3.3V.

The MCP2517FD interfaces directly with microcontrollers operating at 2.7V to 5.5V. In addition, the MCP2517FD connects directly to high-speed CAN FD transceivers. There are no external level shifters required when connecting VDD of the MCP2517FD and the microcontroller to VIO of the transceiver.

The VDD of the CAN FD transceiver is connected to 5V.

The SPI interface is used to configure and control the CAN FD controller.

The MCP2517FD signals interrupts to the microcontroller using INT, INT0 and INT1. Interrupts need to be cleared by the microcontroller through SPI.

The CLKO pin provides the clock to the microcontroller.

## FIGURE 1-2: MCP2517FD INTERFACING WITH A 3.3V MICROCONTROLLER

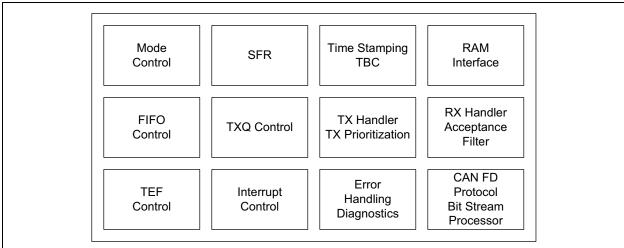

# 2.0 CAN FD CONTROLLER MODULE

Figure 2-1 shows the main blocks of the CAN FD Controller module:

- The CAN FD Controller module has multiple modes:

- Configuration

- Normal CAN FD

- Normal CAN 2.0

- Sleep

- Listen Only

- Restricted Operation

- Internal and External Loop back modes

- The CAN FD Bit Stream Processor (BSP) implements the Medium Access Control of the CAN FD protocol described in ISO11898-1:2015. It serializes and de-serializes the bit stream, encodes and decodes the CAN FD frames, manages the medium access, acknowledges frames, and detects and signals errors.

- The TX Handler prioritizes the messages that are requested for transmission by the Transmit FIFOs. It uses the RAM Interface to fetch the transmit data from RAM and provides it to the BSP for transmission.

- The BSP provides received messages to the RX Handler. The RX Handler uses the Acceptance Filter to filter out messages that shall be stored into Receive FIFOs. It uses the RAM Interface to store received data into RAM.

- Each FIFO can be configured either as a Transmit or Receive FIFO. The FIFO Control keeps track of the FIFO Head and Tail, and calculates the User Address. For a TX FIFO, the User Address points to the address in RAM where the data for the next transmit message shall be stored. For a RX FIFO, the User Address points to the address in RAM where the data of the next receive message shall be read. The User notifies the FIFO that a message was written to or read from RAM by incrementing the Head/Tail of the FIFO.

- The Transmit Queue (TXQ) is a special transmit FIFO that transmits the messages based on the ID of the messages stored in the queue.

- The Transmit Event FIFO (TEF) stores the message IDs of the transmitted messages.

- A free-running Time Base Counter is used to time stamp received messages. Messages in the TEF can also be time stamped.

- The CAN FD Controller module generates interrupts when new messages are received or when messages were transmitted successfully.

- The Special Function Registers (SFR) are used to control and to read the status of the CAN FD Controller module.

Note 1: This data sheet summarizes the features of the CAN FD Controller module. It is not intended to be a comprehensive reference source. To complement the information in this data sheet, refer to the related section of the "MCP2517FD Family Reference Manual".

FIGURE 2-1: CAN FD CONTROLLER MODULE BLOCK DIAGRAM

# MCP2517FD

NOTES:

# 3.0 MEMORY ORGANIZATION

Figure 3-1 illustrates the main sections of the memory and its address ranges:

- MCP2517FD Special Function Registers (SFR)

- CAN FD Controller Module SFR

- Message Memory (RAM)

The SFR are 32 bit wide. The LSB is located at the lower address, e.g., the LSB of C1CON is located at address 0x000, while its MSB is located at address 0x003.

Table 3-1 lists the MCP2517FD specific registers. The first column contains the address of the SFR.

Table 3-2 lists the registers of the CAN FD Controller Module. The first column contains the address of the SFR.

#### FIGURE 3-1: MEMORY MAP

| MSB<br>Address | ◄   | 32                   | bit                                     |     | LSB<br>Address |  |

|----------------|-----|----------------------|-----------------------------------------|-----|----------------|--|

| 0x003          | MSB |                      |                                         | LSB | 0x000          |  |

|                | CAN | FD Control<br>(752 B |                                         | SFR |                |  |

| 0x2EF          |     |                      |                                         |     | 0x2EC          |  |

| 0x2F3          |     | Unimple<br>(272 B    |                                         |     | 0x2F0          |  |

| 0x3FF<br>0x403 |     | (212                 | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     | 0x3FC<br>0x400 |  |

|                |     | RA<br>(2 KB          |                                         |     |                |  |

| 0xBFF<br>0xC03 |     | Unimple<br>(512 B    |                                         |     | 0xBFC<br>0xC00 |  |

| 0xDFF          |     | (012 E               | ,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,,, |     | 0xDFC          |  |

| 0xE03          |     | MCP2517<br>(20 B     |                                         |     | 0xE00          |  |

| 0xE13<br>0xE17 |     | Rese<br>(492 B       |                                         |     | 0xE10<br>0xE14 |  |

| 0xFFF          |     |                      | ,                                       |     | 0xFFC          |  |

| Address            | Name    |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |

|--------------------|---------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|

| E03                | OSC     | 31:24 |                   |                   |                   | —                 | —                 | —                 | —                | _                |  |  |

| E02                |         | 23:16 | _                 | _                 | _                 | _                 | _                 | _                 | _                |                  |  |  |

| E01                |         | 15:8  | _                 | _                 | _                 | SCLKRDY           | _                 | OSCRDY            | —                | PLLRDY           |  |  |

| E00 <sup>(1)</sup> |         | 7:0   |                   | CLKOD             | IV<1:0>           | SCLKDIV           | _                 | OSCDIS            | —                | PLLEN            |  |  |

|                    | IOCON   | 31:24 | _                 | INTOD             | SOF               | TXCANOD           | —                 | —                 | PM1              | PM0              |  |  |

|                    |         | 23:16 | _                 | _                 | _                 | _                 | _                 | _                 | GPI01            | GPIO0            |  |  |

|                    |         | 15:8  | _                 | _                 | _                 | —                 | _                 | _                 | LAT1             | LAT0             |  |  |

| E04                |         | 7:0   |                   | XSTBYEN           | -                 | _                 | _                 | _                 | TRIS1            | TRIS0            |  |  |

|                    | CRC     | 31:24 | _                 | _                 | _                 | _                 | _                 | _                 | FERRIE           | CRCERRIE         |  |  |

|                    |         | 23:16 |                   |                   |                   | —                 | _                 | _                 | FERRIF           | CRCERRIF         |  |  |

|                    |         | 15:8  | CRC<15:8>         |                   |                   |                   |                   |                   |                  |                  |  |  |

| E08                |         | 7:0   |                   |                   |                   | CRC               | <7:0>             |                   |                  |                  |  |  |

|                    | ECCCON  | 31:24 | _                 |                   |                   | —                 |                   |                   | —                |                  |  |  |

|                    |         | 23:16 | _                 | _                 | _                 | —                 | —                 | —                 | _                | _                |  |  |

|                    |         | 15:8  | _                 |                   |                   |                   | PARITY<6:0>       |                   |                  |                  |  |  |

| E0C                |         | 7:0   |                   | -                 | _                 | _                 | _                 | DEDIE             | SECIE            | ECCEN            |  |  |

|                    | ECCSTAT | 31:24 | _                 | _                 | _                 | _                 |                   | ERRADD            | )R<11:8>         |                  |  |  |

|                    |         | 23:16 |                   |                   |                   | ERRADI            | DR<7:0>           |                   |                  |                  |  |  |

|                    |         | 15:8  | _                 | —                 | —                 | —                 | _                 | _                 | —                | _                |  |  |

| E10                |         | 7:0   |                   | -                 | _                 | _                 | _                 | DEDIF             | SECIF            | _                |  |  |

# TABLE 3-1: MCP2517FD REGISTER SUMMARY

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| Addr.              | Name     |       | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2 | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |

|--------------------|----------|-------|-------------------|-------------------|-------------------|-------------------|-------------------|-------------------|------------------|------------------|--|--|--|

| 03                 | C1CON    | 31:24 |                   | TXBWS             | S<3:0>            |                   | ABAT              |                   | REQOP<2:0>       |                  |  |  |  |

| 02                 |          | 23:16 |                   | OPMOD<2:0>        |                   | TXQEN             | STEF              | SERR2LOM          | ESIGM            | RTXAT            |  |  |  |

| 01                 |          | 15:8  | _                 | —                 | _                 | BRSDIS            | BUSY              | WFT               | <1:0>            | WAKFIL           |  |  |  |

| 00 <sup>[ 1]</sup> |          | 7:0   | _                 | PXEDIS            | ISOCRCEN          |                   |                   | DNCNT<4:0>        |                  |                  |  |  |  |

|                    | C1NBTCFG | 31:24 |                   |                   |                   | BRP<              | :7:0>             |                   |                  |                  |  |  |  |

|                    |          | 23:16 |                   |                   |                   | TSEG1             | <7:0>             |                   |                  |                  |  |  |  |

|                    |          | 15:8  | — TSEG2<          |                   |                   |                   |                   |                   |                  |                  |  |  |  |

| 04                 |          | 7:0   | —                 |                   |                   |                   | SJW<6:0>          |                   |                  |                  |  |  |  |

|                    | C1DBTCFG | 31:24 |                   | -                 |                   | BRP<7:0>          |                   |                   |                  |                  |  |  |  |

|                    |          | 23:16 | —                 | —                 | _                 |                   |                   | TSEG1<4:0>        |                  |                  |  |  |  |

|                    |          | 15:8  | —                 | —                 | —                 | —                 |                   | TSEG              | 2<3:0>           |                  |  |  |  |

| 08                 |          | 7:0   | _                 | _                 | _                 | —                 |                   | SJW               | <3:0>            |                  |  |  |  |

|                    | C1TDC    | 31:24 |                   | _                 | —                 | —                 | _                 | _                 | EDGFLTEN         | SID11EN          |  |  |  |

|                    |          | 23:16 | —                 | —                 | —                 | —                 | —                 | —                 | TDCMC            | D<1:0>           |  |  |  |

|                    |          | 15:8  | —                 |                   | -                 |                   | TDCO<6:0>         |                   |                  |                  |  |  |  |

| 0C                 |          | 7:0   | _                 |                   |                   |                   | TDC               | /<5:0>            |                  |                  |  |  |  |

|                    | C1TBC    | 31:24 |                   |                   |                   | TBC<3             | 1:24>             |                   |                  |                  |  |  |  |

|                    |          | 23:16 |                   | TBC<23:16>        |                   |                   |                   |                   |                  |                  |  |  |  |

|                    |          | 15:8  |                   |                   |                   | TBC<              | 15:8>             |                   |                  |                  |  |  |  |

| 10                 |          | 7:0   |                   |                   |                   | TBC<              | 7:0>              |                   |                  |                  |  |  |  |

|                    | C1TSCON  | 31:24 | _                 | _                 | —                 | —                 | —                 | —                 | —                | _                |  |  |  |

|                    |          | 23:16 | _                 | —                 | _                 | _                 | _                 | TSRES             | TSEOF            | TBCEN            |  |  |  |

|                    |          | 15:8  | _                 |                   | —                 | _                 | _                 | -                 | TBCPR            | E<9:8>           |  |  |  |

| 14                 |          | 7:0   | TBCPRE<7:0>       |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|                    | C1VEC    | 31:24 | - RXCODE<6:0>     |                   |                   |                   |                   |                   |                  |                  |  |  |  |

|                    |          | 23:16 | _                 |                   |                   | 7                 | TXCODE<6:0>       |                   |                  |                  |  |  |  |

|                    |          | 15:8  | _                 | —                 | —                 |                   |                   | FILHIT<4:0>       |                  |                  |  |  |  |

| 18                 |          | 7:0   | _                 |                   | -                 |                   |                   |                   |                  |                  |  |  |  |

|                    | C1INT    | 31:24 | IVMIE             | WAKIE             | CERRIE            | SERRIE            | RXOVIE            | TXATIE            | SPICRCIE         | ECCIE            |  |  |  |

|                    |          | 23:16 |                   | —                 | —                 | TEFIE             | MODIE             | TBCIE             | RXIE             | TXIE             |  |  |  |

|                    |          | 15:8  | IVMIF             | WAKIF             | CERRIF            | SERRIF            | RXOVIF            | TXATIF            | SPICRCIF         | ECCIF            |  |  |  |

| 1C                 |          | 7:0   | _                 | —                 | —                 | TEFIF             | MODIF             | TBCIF             | RXIF             | TXIF             |  |  |  |

|                    | C1RXIF   | 31:24 |                   |                   |                   | RFIF<3            |                   |                   |                  |                  |  |  |  |

|                    |          | 23:16 |                   |                   |                   | RFIF<2            |                   |                   |                  |                  |  |  |  |

|                    |          | 15:8  |                   |                   |                   | RFIF<             | 15:8>             |                   |                  |                  |  |  |  |

| 20                 |          | 7:0   |                   |                   |                   | RFIF<7:1>         |                   |                   |                  | —                |  |  |  |

|                    | C1TXIF   | 31:24 |                   |                   |                   | TFIF<3            |                   |                   |                  |                  |  |  |  |

|                    |          | 23:16 |                   |                   |                   | TFIF<2            |                   |                   |                  |                  |  |  |  |

|                    |          | 15:8  |                   |                   |                   | TFIF<             |                   |                   |                  |                  |  |  |  |

| 24                 |          | 7:0   |                   |                   |                   | TFIF<             |                   |                   |                  |                  |  |  |  |

|                    | C1RXOVIF | 31:24 |                   |                   |                   | RFOVIF            |                   |                   |                  |                  |  |  |  |

|                    |          | 23:16 |                   |                   |                   | RFOVIE            |                   |                   |                  |                  |  |  |  |

|                    |          | 15:8  |                   |                   |                   | RFOVIF            | <15:8>            |                   |                  |                  |  |  |  |

| 28                 |          | 7:0   |                   |                   |                   | RFOVIF<7:1>       |                   |                   |                  | _                |  |  |  |

|                    | C1TXATIF | 31:24 |                   |                   |                   | TFATIF<           |                   |                   |                  |                  |  |  |  |

|                    |          | 23:16 |                   |                   |                   | TFATIF<           |                   |                   |                  |                  |  |  |  |

|                    |          | 15:8  |                   |                   |                   | TFATIF            |                   |                   |                  |                  |  |  |  |

| 2C                 |          | 7:0   |                   |                   |                   | TFATIF            | <7:0>             |                   |                  |                  |  |  |  |

| TABLE 3-2: | CAN FD CONTROLLER MODULE REGISTER SUMMARY |

|------------|-------------------------------------------|

|            |                                           |

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| Addr. | Name                    |               | Bit<br>31/23/15/7 | Bit<br>30/22/14/6 | Bit<br>29/21/13/5 | Bit<br>28/20/12/4 | Bit<br>27/19/11/3 | Bit<br>26/18/10/2    | Bit<br>25/17/9/1 | Bit<br>24/16/8/0 |  |  |  |  |

|-------|-------------------------|---------------|-------------------|-------------------|-------------------|-------------------|-------------------|----------------------|------------------|------------------|--|--|--|--|

|       | C1TXREQ                 | 31:24         |                   |                   |                   | TXREQ<            | :31:24>           |                      |                  |                  |  |  |  |  |

|       |                         | 23:16         |                   |                   |                   | TXREQ<            | :23:16>           |                      |                  |                  |  |  |  |  |

|       |                         | 15:8          |                   | TXREQ<15:8>       |                   |                   |                   |                      |                  |                  |  |  |  |  |

| 30    |                         | 7:0           |                   | TXREQ<7:0>        |                   |                   |                   |                      |                  |                  |  |  |  |  |

|       | C1TREC                  | 31:24         | _                 | _                 | _                 | _                 | _                 | _                    | _                |                  |  |  |  |  |

|       |                         | 23:16         | —                 | —                 | TXBO              | TXBP              | RXBP              | TXWARN               | RXWARN           | EWARN            |  |  |  |  |

|       |                         | 15:8          |                   |                   |                   | TEC<              | 7:0>              |                      |                  |                  |  |  |  |  |

| 34    |                         | 7:0           |                   |                   |                   | REC<              | 7:0>              |                      |                  |                  |  |  |  |  |

|       | C1BDIAG0                | 31:24         |                   | DTERRCNT<7:0>     |                   |                   |                   |                      |                  |                  |  |  |  |  |

|       |                         | 23:16         |                   |                   |                   | DRERRC            | NT<7:0>           |                      |                  |                  |  |  |  |  |

|       |                         | 15:8          |                   |                   |                   | NTERRC            | NT<7:0>           |                      |                  |                  |  |  |  |  |

| 38    |                         | 7:0           |                   |                   |                   | NRERRC            | NT<7:0>           |                      |                  |                  |  |  |  |  |

|       | C1BDIAG1                | 31:24         | DLCMM             | ESI               | DCRCERR           |                   | DFORMERR          | _                    | DBIT1ERR         | DBIT0ERR         |  |  |  |  |

|       |                         | 23:16         | TXBOERR           | —                 | NCRCERR           | NSTUFERR          | NFORMERR          | NACKERR              | NBIT1ERR         | NBIT0ERR         |  |  |  |  |

|       |                         | 15:8          |                   |                   |                   | EFMSGC            | NT<15:8>          |                      |                  |                  |  |  |  |  |

| 3C    |                         | 7:0           |                   | EFMSGCNT<7:0>     |                   |                   |                   |                      |                  |                  |  |  |  |  |

|       | C1TEFCON                | 31:24         | -                 | —                 | —                 |                   |                   | FSIZE<4:0>           | i                | i                |  |  |  |  |

|       |                         | 23:16         | —                 |                   | —                 | —                 | —                 | —                    | —                | —                |  |  |  |  |

|       |                         | 15:8          | _                 | —                 | _                 | _                 | _                 | FRESET               | —                | UINC             |  |  |  |  |

| 40    |                         | 7:0           | _                 |                   | TEFTSEN           | _                 | TEFOVIE           | TEFFIE               | TEFHIE           | TEFNEIE          |  |  |  |  |

|       | C1TEFSTA                | 31:24         | _                 | —                 | —                 | _                 | _                 |                      | —                | —                |  |  |  |  |

|       |                         | 23:16         | _                 | —                 | _                 | _                 | _                 |                      | _                | _                |  |  |  |  |

|       |                         | 15:8          | _                 | —                 | _                 | _                 | —                 | —                    | —                | —                |  |  |  |  |

| 44    |                         | 7:0           | _                 | _                 | _                 |                   | TEFOVIF           | TEFFIF               | TEFHIF           | TEFNEIF          |  |  |  |  |

|       | C1TEFUA                 | 31:24         |                   | TEFUA<31:24>      |                   |                   |                   |                      |                  |                  |  |  |  |  |

|       |                         | 23:16         |                   |                   |                   | TEFUA<            |                   |                      |                  |                  |  |  |  |  |

|       |                         | 15:8          |                   |                   |                   | TEFUA             |                   |                      |                  |                  |  |  |  |  |

| 48    |                         | 7:0           |                   |                   |                   | TEFUA             |                   |                      |                  |                  |  |  |  |  |

|       | Reserved <sup>(2)</sup> | 31:24         |                   |                   |                   | Reserved          |                   |                      |                  |                  |  |  |  |  |

|       |                         | 23:16         |                   |                   |                   | Reserved          |                   |                      |                  |                  |  |  |  |  |

| 10    |                         | 15:8          |                   |                   |                   | Reserved          |                   |                      |                  |                  |  |  |  |  |

| 4C    | OUTVOOON                | 7:0           |                   |                   |                   | Reserve           | d<7:U>            | 50175 .4 0           |                  |                  |  |  |  |  |

|       | C1TXQCON                | 31:24         |                   | PLSIZE<2:0>       | <1.0>             |                   |                   | FSIZE<4:0>           |                  |                  |  |  |  |  |

|       |                         | 23:16<br>15:8 | _                 | TXAT              | <1.0>             |                   |                   | TXPRI<4:0><br>FRESET | TXREQ            | UINC             |  |  |  |  |

| 50    |                         | 7:0           | TXEN              |                   |                   | TXATIE            |                   | TXQEIE               |                  | TXQNIE           |  |  |  |  |

| 50    | C1TXQSTA                | 31:24         | IALIN             |                   | _                 |                   |                   |                      |                  | TAQNIL           |  |  |  |  |

|       | UTINGUIA                | 23:16         | _                 |                   |                   |                   |                   |                      |                  |                  |  |  |  |  |

|       |                         | 15:8          | _                 | _                 |                   |                   |                   | TXQCI<4:0>           |                  |                  |  |  |  |  |

| 54    |                         | 7:0           | TXABT             | TXLARB            | TXERR             | TXATIF            | _                 | TXQEIF               | _                | TXQNIF           |  |  |  |  |

| ~ 1   | C1TXQUA                 | 31:24         |                   |                   |                   | TXQUA<            | :31:24>           |                      |                  |                  |  |  |  |  |

|       |                         | 23:16         |                   |                   |                   | TXQUA             |                   |                      |                  |                  |  |  |  |  |

|       |                         | 15:8          |                   |                   |                   | TXQUA             |                   |                      |                  |                  |  |  |  |  |

| 58    |                         | 7:0           |                   |                   |                   | TXQUA             |                   |                      |                  |                  |  |  |  |  |

# TABLE 3-2: CAN FD CONTROLLER MODULE REGISTER SUMMARY (CONTINUED)

Note 1: The lower order byte of the 32-bit register resides at the low-order address.

| Name                               |                 | Bit<br>31/23/15/7                                                                               | Bit<br>30/22/14/6                                 | Bit<br>29/21/13/5                                  | Bit<br>28/20/12/4                                  | Bit<br>27/19/11/3                                                                | Bit<br>26/18/10/2                                                                                                                                      | Bit<br>25/17/9/1                                                                                                                                       | Bit<br>24/16/8/0                                                                                                                                       |  |  |

|------------------------------------|-----------------|-------------------------------------------------------------------------------------------------|---------------------------------------------------|----------------------------------------------------|----------------------------------------------------|----------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| C1FIFOCON1                         | 31:24           |                                                                                                 | PLSIZE<2:0>                                       |                                                    |                                                    |                                                                                  | FSIZE<4:0>                                                                                                                                             |                                                                                                                                                        |                                                                                                                                                        |  |  |

|                                    | 23:16           | —                                                                                               | TXAT                                              | <1:0>                                              |                                                    | -                                                                                | TXPRI<4:0>                                                                                                                                             |                                                                                                                                                        |                                                                                                                                                        |  |  |

|                                    | 15:8            | —                                                                                               | _                                                 | —                                                  | —                                                  | —                                                                                | FRESET                                                                                                                                                 | TXREQ                                                                                                                                                  | UINC                                                                                                                                                   |  |  |

|                                    | 7:0             | TXEN                                                                                            | RTREN                                             | RXTSEN                                             | TXATIE                                             | RXOVIE                                                                           | TFERFFIE                                                                                                                                               | TFHRFHIE                                                                                                                                               | TFNRFNI                                                                                                                                                |  |  |

| C1FIFOSTA1                         | 31:24           | _                                                                                               |                                                   | _                                                  | —                                                  | _                                                                                | _                                                                                                                                                      | _                                                                                                                                                      | _                                                                                                                                                      |  |  |

|                                    | 23:16           | _                                                                                               |                                                   | _                                                  | _                                                  | _                                                                                | _                                                                                                                                                      | _                                                                                                                                                      |                                                                                                                                                        |  |  |

|                                    | 15:8            | :8 — — — FIFOCI<4:0>                                                                            |                                                   |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

|                                    | 7:0             | TXABT                                                                                           | TXLARB                                            | TXERR                                              | TXATIF                                             | RXOVIF                                                                           | TFERFFIF                                                                                                                                               | TFHRFHIF                                                                                                                                               | TFNRFNI                                                                                                                                                |  |  |

| C1FIFOUA1                          | 31:24           |                                                                                                 | FIFOUA<31:24>                                     |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

|                                    | 23:16           |                                                                                                 | FIFOUA<23:16>                                     |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

|                                    | 15:8            | FIFOUA<15:8>                                                                                    |                                                   |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

|                                    | 7:0             |                                                                                                 |                                                   |                                                    | FIFOUA                                             | <7:0>                                                                            |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON2                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA2                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA2                          | 31:0            |                                                                                                 |                                                   |                                                    | same as C                                          |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON3                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA3                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA3                          | 31:0            |                                                                                                 |                                                   |                                                    | same as C                                          |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON4                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA4                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA4                          | 31:0            |                                                                                                 |                                                   |                                                    | same as C                                          |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON5                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA5                         | 31:0            |                                                                                                 |                                                   |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA5                          | 31:0            |                                                                                                 | same as C1FIFOSTA1                                |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON6                         | 31:0            |                                                                                                 | same as C1FIFOUA1 same as C1FIFOCON1              |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA6                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA6                          | 31:0            |                                                                                                 |                                                   |                                                    | same as Cr                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON7                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON7                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

|                                    | 31:0            |                                                                                                 |                                                   |                                                    | same as Cr                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA7                          |                 |                                                                                                 |                                                   |                                                    |                                                    |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON8                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA8                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA8                          | 31:0            |                                                                                                 |                                                   |                                                    | same as C                                          |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON9                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA9                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA9                          | 31:0            |                                                                                                 |                                                   |                                                    | same as C                                          |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON10                        |                 |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA10                        |                 |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA10                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C                                          |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON11                        |                 |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOSTA11                        | 31:0            |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOUA11                         | 31:0            |                                                                                                 |                                                   |                                                    | same as C                                          |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

| C1FIFOCON12                        |                 |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |

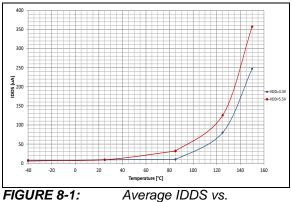

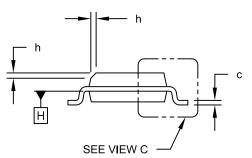

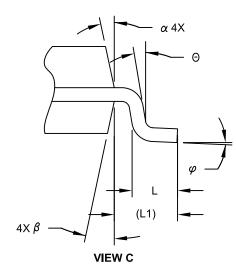

| C1FIFOSTA12                        |                 |                                                                                                 |                                                   |                                                    | same as C1                                         |                                                                                  |                                                                                                                                                        |                                                                                                                                                        |                                                                                                                                                        |  |  |