#### Hi3670 V100 Application Processor

## **Data Sheet**

Issue 01 Date 2018-03-02

#### Copyright © HiSilicon Technologies Co., Ltd. 2018. All rights reserved.

No part of this document may be reproduced or transmitted in any form or by any means without prior written consent of HiSilicon Technologies Co., Ltd.

#### **Trademarks and Permissions**

, HISILICON, and other HiSilicon icons are trademarks of HiSilicon Technologies Co., Ltd.

All other trademarks and trade names mentioned in this document are the property of their respective holders.

#### Notice

The purchased products, services and features are stipulated by the contract made between HiSilicon and the customer. All or part of the products, services and features described in this document may not be within the purchase scope or the usage scope. Unless otherwise specified in the contract, all statements, information, and recommendations in this document are provided "AS IS" without warranties, guarantees or representations of any kind, either express or implied.

The information in this document is subject to change without notice. Every effort has been made in the preparation of this document to ensure accuracy of the contents, but all statements, information, and recommendations in this document do not constitute a warranty of any kind, express or implied.

#### HiSilicon Technologies Co., Ltd.

- Address: Huawei Industrial Base Bantian, Longgang Shenzhen 518129 People's Republic of China

- Website: http://www.hisilicon.com

- Email: support@hisilicon.com

## **About This Document**

### Purpose

This document describes the basic functions and specifications of the Hi3670 V100.

#### **Related Version**

The following table lists the product version related to this document.

| Product Name | Version |

|--------------|---------|

| Hi3670       | V100    |

#### **Intended Audience**

This document is intended for:

- Technical support engineers

- Board hardware development engineers

- Software engineers

#### **Symbol Conventions**

The symbols that may be found in this document are defined as follows.

| Symbol | Description                                                                                                                                                                   |  |

|--------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|        | Alerts you to a potentially hazardous situation that could, if<br>not avoided, result in equipment damage, data loss,<br>performance deterioration, or unanticipated results. |  |

|        | Provides additional information to emphasize or supplement important points in the main text.                                                                                 |  |

## **Change History**

Changes between document issues are cumulative. The latest document issue contains all the changes made in earlier issues.

#### Issue 01 (2018-03-02)

This issue is the first official release

## Contents

| About This Document        | ii |

|----------------------------|----|

| 1 Introduction             | 1  |

| 1.1 Major Features         |    |

| 1.1.1 Computing Capability |    |

| 1.1.2 Multimedia           |    |

| 1.1.3 Interfaces           |    |

| 1.2 Chip Architecture      |    |

| 1.3 Typical Application    |    |

| 2 Description              | 5  |

| 2.1 Interrupt              |    |

| 2.1.1 Function Description |    |

| 2.1.2 Interrupt Mapping    |    |

| 2.2 Memory Mapping         | 7  |

| 3 Mobile Processing Module |    |

| 3.1 CPU                    |    |

| 3.1.1 Overview             |    |

| 3.1.2 Operating Mode       |    |

| 3.2 GPU                    |    |

| 3.2.1 Overview             |    |

| 3.2.2 Operating Mode       |    |

| 3.3 I/O Processor          |    |

| 4 Media Processing         |    |

| 4.1 Overview               |    |

| 4.2 VENC                   |    |

| 4.3 VDEC                   |    |

| 4.3.1 Function Description |    |

| 4.3.2 Clock and Reset      |    |

| 4.4 ICS                    |    |

| 4.4.1 Function Description |    |

| 4.4.2 Clock and Reset      |    |

| 4.5 DSS                    |    |

| 4.5.1 Function Description |    |

|----------------------------|----|

| 4.5.2 Clock and Reset      |    |

| 4.5.3 Application          |    |

| 4.5.4 DP (DSS)             |    |

| 4.6 ASP                    |    |

| 4.6.1 DSP                  |    |

| 4.6.2 DMAC                 |    |

| 4.6.3 SIO                  |    |

| 4.6.4 WatchDog             |    |

| 4.6.5 GPIO                 |    |

| 4.6.6 Timer                |    |

| 4.6.7 IPC                  |    |

| 4.6.8 OCRAM                |    |

| 4.6.9 DP (ASP)             |    |

| 5 Storage Control          | 65 |

| 5.1 Overview               |    |

| 5.2 Storage Solution       |    |

| 5.3 SD/SDIO                |    |

| 5.4 UFS                    |    |

| 6 Interface Control        |    |

| 6.1 USB                    |    |

| 6.2 UART                   |    |

| 6.3 SPI                    |    |

| 6.4 I <sup>2</sup> C       |    |

| 6.5 GPIO                   |    |

| 6.6 PWM                    |    |

| 6.7 PCIe                   |    |

|                            |    |

## **1** Introduction

## **1.1 Major Features**

#### 1.1.1 Computing Capability

Core specifications of the Hi3670 computing capability are as follows:

- 8-core CPU, including four 2.36 GHz ARM Cortex-A73 MPCore high-performance cores and four 1.8 GHz ARM Cortex-A53 MPCore energy-efficient cores

- OPENGL ES3.2, OPENCL 1.2, OPENCL 2.0, Renderscript, and high-performance 3D acceleration technologies compressed by AFBC

- MMU management for all chip channels, reducing overhead of reserved memories

- 1866 MHz four-channel LPDDR4x

- AFBC compression and process optimization to reduce the DDR bandwidth

- Hardware acceleration for secure encryption and decryption using dual engines

#### 1.1.2 Multimedia

Core specifications of the Hi3670 multimedia features are as follows:

- Built-in video hardware decoder (with the maximum rate of H.265 3840 x 2160@60 fps/H.264 3840 x 2160@30 fps)

- Built-in video hardware encoder (H.265/H.264 3840 x 2160@30 fps)

- Built-in Mali-G72 MP12 GPU

- Independent JPG codec and face detection acceleration module

- Maximum resolution of 3840 x 2400@60 Hz)

- Dual MIPI display interfaces

Table 1-1 describes the multimedia features of the Hi3670.

#### Table 1-1 Hi3670 multimedia features

| Multimedia Feature | Description |

|--------------------|-------------|

| GPU                |             |

| Multimedia Feature                             | Description                                                                                                                                                                                                                                                             |  |  |

|------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| 3D acceleration                                | • Supports OpenGL ES 1.1 and 2.0, OpenGL ES 3.0, OpenGL ES 3.1, and OpenGL ES 3.2.                                                                                                                                                                                      |  |  |

|                                                | • Supports OpenCL 1.1, 1.2, and 2.0.                                                                                                                                                                                                                                    |  |  |

|                                                | • Renderscript                                                                                                                                                                                                                                                          |  |  |

|                                                | • Vulkan 1.0                                                                                                                                                                                                                                                            |  |  |

| Camera input interface                         | Three MIPI CSI interfaces (D-PHY 4+4+4 lane or C-PHY 3+3+3 lane)                                                                                                                                                                                                        |  |  |

| Image input format                             | <ol> <li>Supports uncompressed RAW10, RAW12, and RAW14.</li> <li>Supports RGB-IR input RAW10, RAW12, and RAW14 (2 MPs at 120 fps at most).</li> <li>Supports phase data sensors.</li> <li>Supports uncommon formats after storage conversion in bypass mode.</li> </ol> |  |  |

| Storage format                                 | Supports RAW10, RAW12, and RAW14. Data in these formats is stored in 2-byte alignment.                                                                                                                                                                                  |  |  |

| 3A                                             | Supports auto focus (AF), auto white balance (AWB), and auto exposure (AE).                                                                                                                                                                                             |  |  |

| Display                                        |                                                                                                                                                                                                                                                                         |  |  |

| Display pixel depth                            | RGB888 or RGB565                                                                                                                                                                                                                                                        |  |  |

| Display resolution                             | The maximum resolution is 3840 x 2400, with the refresh rate of 60 Hz.                                                                                                                                                                                                  |  |  |

| MIPI interface                                 | Supports dual MIPI display interfaces.                                                                                                                                                                                                                                  |  |  |

| Display system                                 | • Supports online multi-layer overlay, color key, alpha blending, and DIM.                                                                                                                                                                                              |  |  |

|                                                | • Supports online resizing and offline resizing and rotation.                                                                                                                                                                                                           |  |  |

|                                                | • Supports the interface IFBC, IFBC and RSP integration, and VESA compression algorithms.                                                                                                                                                                               |  |  |

|                                                | • Supports online display post processing and color management.                                                                                                                                                                                                         |  |  |

|                                                | • Supports offline overlay for multiple layers, color key, alpha blending, and DIM.                                                                                                                                                                                     |  |  |

|                                                | Supports bus data compression and decompression.                                                                                                                                                                                                                        |  |  |

| Encoding and decoding                          |                                                                                                                                                                                                                                                                         |  |  |

| Video encoding Encoding format: H.265 or H.264 |                                                                                                                                                                                                                                                                         |  |  |

|                                                | HD photographing: 3840 x 2400@30 fps                                                                                                                                                                                                                                    |  |  |

|                                                | 4 x 1080p@30 fps simultaneous HD encoding                                                                                                                                                                                                                               |  |  |

|                                                | 720p 240 fps video, supporting fast recording and slow playback                                                                                                                                                                                                         |  |  |

| Video decoding                                 | • Supports multiple formats such as H.265 M10P@L5.1 and H.264 BP/MP/HP@L5.1.                                                                                                                                                                                            |  |  |

|                                                | • Up to H.265 4K@60 fps and H.264 4K@30 fps                                                                                                                                                                                                                             |  |  |

| Audio                                          |                                                                                                                                                                                                                                                                         |  |  |

| Audio interface                                | Supports I <sup>2</sup> S and PCM interfaces.                                                                                                                                                                                                                           |  |  |

| Audio sampling rate                            | 8 kHz, 16 kHz, 32 kHz, 48 kHz, 96 kHz, or 192 kHz                                                                                                                                                                                                                       |  |  |

| Audio DSP                                      | The HiFi3 DSP is used to process audio data.                                                                                                                                                                                                                            |  |  |

#### 1.1.3 Interfaces

Table 1-2 describes the peripheral interfaces of the Hi3670.

#### Table 1-2 Peripheral interfaces of the Hi3670

| Interface Name          | Description                                                                                                                                      |  |  |

|-------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------|--|--|

| USB interface           | 1. Supports the USB 3.0 over Type-C interface.                                                                                                   |  |  |

|                         | 2. Supports BC1.2 battery charging.                                                                                                              |  |  |

| PCIe interface          | Supports PCIe1.1/x1.                                                                                                                             |  |  |

| Micro SD card interface | Supports SD 3.0 or SD 2.0 card.                                                                                                                  |  |  |

| I2C interface           | Supports the high-speed I2C interface.                                                                                                           |  |  |

| SPI                     | A maximum of 40 MHz (SPI3) is supported. For details about the frequency supported by the SPIs 0 to 4 in various scenarios, see section 8.3 SPI. |  |  |

| UART interface          | Supports the high-speed UART interface.                                                                                                          |  |  |

| GPIO interface          | Supports various GPIO interfaces.                                                                                                                |  |  |

Table 1-3 describes the memory interfaces of the Hi3670.

Table 1-3

Hi3670

memory interfaces

| Interface Name | Description                   |  |

|----------------|-------------------------------|--|

| Flash          | Supports UFS 2.0 and UFS 2.1. |  |

| DRAM           | LPDDR4x: 1866 MHz             |  |

Table 1-4 describes the debugging interfaces of the Hi3670.

| Interface Name | Description                                                                     |

|----------------|---------------------------------------------------------------------------------|

| JTAG interface | The Hi3670 provides JTAG debugging interfaces that comply with IEEE Std 1149.1. |

## **1.2 Chip Architecture**

The Hi3670 uses the 10 nm fin field-effect transistor (FinFET) technology of TSMC, and features multiple cores, multiple modes, high performance, and high integration. The Hi3670 provides high-speed mobile computing capability, integrates rich multimedia processing functions and high-level communications processing functions, and adopts the industry-leading low power consumption technology, making it the core SoC chip of the Kirin 970 solution for high-end smartphones.

## **1.3 Typical Application**

The Hi3670 is applied to products such as smartphones and tablets.

# **2** Description

## 2.1 Interrupt

#### 2.1.1 Function Description

The ACPU uses the GIC to handle and control interrupts. Other microcontrollers and media and communication processors have their own interrupt handling logic. This section describes the basic interrupt handling functions of the GIC.

The GIC has the following basic features:

- Supports interrupt nesting.

- Manages the multi-core interrupt distribution.

- Supports security extension.

- Supports query of the states of interrupt sources.

- Provides a unique ID for each interrupt.

- Supports configurable interrupt trigger mode: high-level-triggered mode or edge-triggered mode.

- Sets the priority of each interrupt.

- Generates software interrupts.

#### 2.1.2 Interrupt Mapping

Table 2-1 describes interrupt sources and interrupt signals of the GIC.

| Interrupt Source | GIC Interrupt<br>ID | Interrupt Source       | GIC Interrupt<br>ID |

|------------------|---------------------|------------------------|---------------------|

| A73_interr       | 32                  | intr_ipc_ns_ao[1]      | 205                 |

| A73_exterr       | 33                  | intr_lpmcu_wdog        | 206                 |

| A73_pmu0         | 34                  | -CCI400_err            | 207                 |

| A73_pmu1         | 35                  | -&CCI400_overflow[6:0] | 208                 |

| A73_pmu2         | 36                  | -CCI400_overflow[7]    | 209                 |

#### Table 2-1 GIC interrupt allocation

| Interrupt Source | GIC Interrupt<br>ID | Interrupt Source | GIC Interrupt<br>ID |

|------------------|---------------------|------------------|---------------------|

| A73_pmu3         | 37                  | IPC_S_int0       | 210                 |

| A73_cti0         | 38                  | IPC_S_int1       | 211                 |

| A73_cti1         | 39                  | IPC_S_int4       | 212                 |

| A73_cti2         | 40                  | IPC_S_mbx0       | 213                 |

| A73_cti3         | 41                  | IPC_S_mbx1       | 214                 |

| A73_COMMRX0      | 42                  | IPC_S_mbx2       | 215                 |

| A73_COMMRX1      | 43                  | IPC_S_mbx3       | 216                 |

| A73_COMMRX2      | 44                  | IPC_S_mbx4       | 217                 |

| A73_COMMRX3      | 45                  | IPC_S_mbx5       | 218                 |

| A73_COMMTX0      | 46                  | IPC_S_mbx6       | 219                 |

| A73_COMMTX1      | 47                  | IPC_S_mbx7       | 220                 |

| A73_COMMTX2      | 48                  | IPC_S_mbx8       | 221                 |

| A73_COMMTX3      | 49                  | IPC_S_mbx9       | 222                 |

| A73_COMMIRQ0     | 50                  | IPC_S_mbx18      | 223                 |

| A73_COMMIRQ1     | 51                  | IPC_NS_int0      | 224                 |

| A73_COMMIRQ2     | 52                  | IPC_NS_int1      | 225                 |

| A73_COMMIRQ3     | 53                  | IPC_NS_int4      | 226                 |

| A53_interr       | 54                  | IPC_NS_int5      | 227                 |

| A53_exterr       | 55                  | IPC_NS_int6      | 228                 |

| A53_pmu0         | 56                  | IPC_NS_mbx0      | 229                 |

| A53_pmu1         | 57                  | IPC_NS_mbx1      | 230                 |

| A53_pmu2         | 58                  | IPC_NS_mbx2      | 231                 |

| A53_pmu3         | 59                  | IPC_NS_mbx3      | 232                 |

| A53_cti0         | 60                  | IPC_NS_mbx4      | 233                 |

| A53_cti1         | 61                  | IPC_NS_mbx5      | 234                 |

| A53_cti2         | 62                  | IPC_NS_mbx6      | 235                 |

| A53_cti3         | 63                  | IPC_NS_mbx7      | 236                 |

| A53_COMMRX0      | 64                  | IPC_NS_mbx8      | 237                 |

| A53_COMMRX1      | 65                  | IPC_NS_mbx9      | 238                 |

| A53_COMMRX2      | 66                  | IPC_NS_mbx18     | 239                 |

| Interrupt Source | GIC Interrupt<br>ID | Interrupt Source  | GIC Interrupt<br>ID |

|------------------|---------------------|-------------------|---------------------|

| A53_COMMRX3      | 67                  | Reserved          | 240                 |

| A53_COMMTX0      | 68                  | Reserved          | 241                 |

| A53_COMMTX1      | 69                  | ASP-IPC-ARM       | 242                 |

| A53_COMMTX2      | 70                  | Reserved          | 243                 |

| A53_COMMTX3      | 71                  | Reserved          | 244                 |

| A53_COMMIRQ0     | 72                  | intr_asp_watchdog | 245                 |

| A53_COMMIRQ1     | 73                  | ASP_AXI_DLOCK     | 246                 |

| A53_COMMIRQ2     | 74                  | Reserved          | 247                 |

| A53_COMMIRQ3     | 75                  | Reserved          | 248                 |

## 2.2 Memory Mapping

Table 2-2 lists the address ranges of the ACPU of the Hi3670.

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xFFFF0000-0xFFFFFFFF | 64K                   | Reserved          |

| 0xFFFE0000-0xFFFEFFFF | 64K                   | Reserved          |

| 0xFFFC0000–0xFFFDFFFF | 128K                  | DMSS              |

| 0xFFFB0000–0xFFFBFFFF | 64K                   | Reserved          |

| 0xFFFA0000–0xFFFAFFFF | 64K                   | Reserved          |

| 0xFFF80000–0xFFF9FFFF | 128K                  | Reserved          |

| 0xFFF7E000–0xFFF7FFFF | 8K                    | Reserved          |

| 0xFFF62000–0xFFF7DFFF | 112K                  | Reserved          |

| 0xFFF50000–0xFFF61FFF | 72K                   | Reserved          |

| 0xFFF40000–0xFFF4FFFF | 64K                   | Reserved          |

| 0xFFF3F000–0xFFF3FFFF | 4K                    | Reserved          |

| 0xFFF3E000–0xFFF3EFFF | 4K                    | LP_TIMER          |

| 0xFFF3D000–0xFFF3DFFF | 4K                    | LP_WDG            |

| 0xFFF3A000–0xFFF3CFFF | 12K                   | Reserved          |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xFFF39000–0xFFF39FFF | 4K                    | Reserved          |

| 0xFFF38000–0xFFF38FFF | 4K                    | Reserved          |

| 0xFFF37000–0xFFF37FFF | 4K                    | Reserved          |

| 0xFFF36000–0xFFF36FFF | 4K                    | PMU_I2C1          |

| 0xFFF35000–0xFFF35FFF | 4K                    | PERI_CRG          |

| 0xFFF34000–0xFFF34FFF | 4K                    | PMU_SSI0          |

| 0xFFF33000–0xFFF33FFF | 4K                    | PMU_I2C0          |

| 0xFFF32000–0xFFF32FFF | 4K                    | UART6             |

| 0xFFF31000–0xFFF31FFF | 4K                    | РМС               |

| 0xFFF30000–0xFFF30FFF | 4K                    | TSENSORC          |

| 0xFFF2F000–0xFFF2FFFF | 4K                    | Reserved          |

| 0xFFF2B000–0xFFF2EFFF | 16K                   | Reserved          |

| 0xFFF2A000–0xFFF2AFFF | 4K                    | SPI3              |

| 0xFFF29000–0xFFF29FFF | 4K                    | GPIO19            |

| 0xFFF28000–0xFFF28FFF | 4K                    | GPIO18            |

| 0xFFF24000–0xFFF27FFF | 16K                   | SPMI              |

| 0xFFF23000–0xFFF23FFF | 4K                    | Reserved          |

| 0xFFF22000–0xFFF22FFF | 4K                    | AO_IPC_NS         |

| 0xFFF21000–0xFFF21FFF | 4K                    | Reserved          |

| 0xFFF20000–0xFFF20FFF | 4K                    | Reserved          |

| 0xFFF1F000–0xFFF1FFFF | 4K                    | Reserved          |

| 0xFFF1E000–0xFFF1EFFF | 4K                    | Reserved          |

| 0xFFF1D000–0xFFF1DFFF | 4K                    | GPIO28            |

| 0xFFF1C000–0xFFF1CFFF | 4K                    | TIMER8            |

| 0xFFF1B000–0xFFF1BFFF | 4K                    | TIMER7            |

| 0xFFF1A000–0xFFF1AFFF | 4K                    | TIMER6            |

| 0xFFF19000–0xFFF19FFF | 4K                    | TIMER5            |

| 0xFFF18000–0xFFF18FFF | 4K                    | TIMER4            |

| 0xFFF17000–0xFFF17FFF | 4K                    | TIMER3            |

| 0xFFF16000–0xFFF16FFF | 4K                    | TIMER2            |

| 0xFFF15000–0xFFF15FFF | 4K                    | TIMER1            |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xFFF14000–0xFFF14FFF | 4K                    | TIMER0            |

| 0xFFF12000–0xFFF13FFF | 8K                    | BB_DRX            |

| 0xFFF11000–0xFFF11FFF | 4K                    | AO_IOC            |

| 0xFFF10000–0xFFF10FFF | 4K                    | GPIO27            |

| 0xFFF0F000–0xFFF0FFFF | 4K                    | GPIO26            |

| 0xFFF0E000–0xFFF0EFFF | 4K                    | GPIO25            |

| 0xFFF0D000–0xFFF0DFFF | 4K                    | GPIO24            |

| 0xFFF0C000–0xFFF0CFFF | 4K                    | GPIO23            |

| 0xFFF0B000–0xFFF0BFFF | 4K                    | GPIO22            |

| 0xFFF0A000–0xFFF0AFFF | 4K                    | SCTRL             |

| 0xFFF08000–0xFFF09FFF | 8K                    | SYS_CNT           |

| 0xFFF07000–0xFFF07FFF | 4K                    | Reserved          |

| 0xFFF06000–0xFFF06FFF | 4K                    | Reserved          |

| 0xFFF05000–0xFFF05FFF | 4K                    | RTC1              |

| 0xFFF04000–0xFFF04FFF | 4K                    | RTC0              |

| 0xFFF03000–0xFFF03FFF | 4K                    | Reserved          |

| 0xFFF02000–0xFFF02FFF | 4K                    | Reserved          |

| 0xFFF01000–0xFFF01FFF | 4K                    | Reserved          |

| 0xFFF00000–0xFFF00FFF | 4K                    | Reserved          |

| 0xFFE00000–0xFFEFFFFF | 1M                    | Reserved          |

| 0xFFD80000–0xFFDFFFFF | 512K                  | Reserved          |

| 0xFFD7F000–0xFFD7FFFF | 4K                    | Reserved          |

| 0xFFD7E000–0xFFD7EFFF | 4K                    | Reserved          |

| 0xFFD7D000–0xFFD7DFFF | 4K                    | Reserved          |

| 0xFFD7C000–0xFFD7CFFF | 4K                    | Reserved          |

| 0xFFD7B000–0xFFD7BFFF | 4K                    | IOMCU_GPIO3       |

| 0xFFD7A000–0xFFD7AFFF | 4K                    | IOMCU_GPIO2       |

| 0xFFD79000–0xFFD79FFF | 4K                    | IOMCU_GPIO1       |

| 0xFFD78000–0xFFD78FFF | 4K                    | IOMCU_GPIO0       |

| 0xFFD77000–0xFFD77FFF | 4K                    | IOMCU_DMAC        |

| 0xFFD76000–0xFFD76FFF | 4K                    | IOMCU_UART7       |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xFFD75000–0xFFD75FFF | 4K                    | IOMCU_BLPWM       |

| 0xFFD74000–0xFFD74FFF | 4K                    | IOMCU_UART3       |

| 0xFFD73000–0xFFD73FFF | 4K                    | IOMCU_I2C2        |

| 0xFFD72000–0xFFD72FFF | 4K                    | IOMCU_I2C1        |

| 0xFFD71000–0xFFD71FFF | 4K                    | IOMCU_I2C0        |

| 0xFFD70000–0xFFD70FFF | 4K                    | IOMCU_SPI0        |

| 0xFFD6F000–0xFFD6FFFF | 4K                    | Reserved          |

| 0xFFD6E000–0xFFD6EFFF | 4K                    | Reserved          |

| 0xFFD6C000–0xFFD6DFFF | 8K                    | Reserved          |

| 0xFFD6B000–0xFFD6BFFF | 4K                    | Reserved          |

| 0xFFD6A000–0xFFD6AFFF | 4K                    | IOMCU_I2C3        |

| 0xFFD69000–0xFFD69FFF | 4K                    | IOMCU_UART8       |

| 0xFFD68000–0xFFD68FFF | 4K                    | IOMCU_SPI2        |

| 0xFFD67000–0xFFD67FFF | 4K                    | Reserved          |

| 0xFFD66000–0xFFD66FFF | 4K                    | IOMCU_TIMER2      |

| 0xFFD65000–0xFFD65FFF | 4K                    | IOMCU_I3C         |

| 0xFFD08000–0xFFD64FFF | 372K                  | Reserved          |

| 0xFFD03000–0xFFD07FFF | 20K                   | Reserved          |

| 0xFFD01000–0xFFD02FFF | 8K                    | Reserved          |

| 0xFFD00000–0xFFD00FFF | 4K                    | Reserved          |

| 0xFF800000–0xFFCFFFFF | 5M                    | Reserved          |

| 0xFF400000–0xFF7FFFFF | 4M                    | ICS               |

| 0xFF3E1000–0xFF3FFFFF | 124K                  | Reserved          |

| 0xFF3E0000–0xFF3E0FFF | 4K                    | UFS_SYS_CTRL      |

| 0xFF3C0000–0xFF3DFFFF | 128K                  | UFS_CFG           |

| 0xFF380000–0xFF3BFFFF | 256K                  | Reserved          |

| 0xFF37F000–0xFF37FFFF | 4K                    | SD3               |

| 0xFF37E000–0xFF37EFFF | 4K                    | IOC_MMC0          |

| 0xFF37D000–0xFF37DFFF | 4K                    | MMC0_SYS_CTRL     |

| 0xFF360000–0xFF37CFFF | 116K                  | Reserved          |

| 0xFF340000–0xFF35FFFF | 128K                  | DP_CTRL           |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xFF300000–0xFF33FFFF | 256K                  | Reserved          |

| 0xFF201000–0xFF2FFFFF | 1020K                 | Reserved          |

| 0xFF200000-0xFF200FFF | 4K                    | USB3OTG_BC        |

| 0xFF100000–0xFF1FFFFF | 1M                    | USB3OTG           |

| 0xFF080000–0xFF0FFFFF | 512K                  | Reserved          |

| 0xFF060000–0xFF07FFFF | 128K                  | Reserved          |

| 0xFF050000–0xFF05FFFF | 64K                   | Reserved          |

| 0xFF040000–0xFF04FFFF | 64K                   | Reserved          |

| 0xFF038000–0xFF03FFFF | 32K                   | Reserved          |

| 0xFF034000-0xFF037FFF | 16K                   | Reserved          |

| 0xFF032000–0xFF033FFF | 8K                    | Reserved          |

| 0xFF030000-0xFF031FFF | 8K                    | Reserved          |

| 0xFF013000–0xFF02FFFF | 116K                  | Reserved          |

| 0xFF012000–0xFF012FFF | 4K                    | Reserved          |

| 0xFF011000–0xFF011FFF | 4K                    | Reserved          |

| 0xFF010000–0xFF010FFF | 4K                    | Reserved          |

| 0xFF00F000–0xFF00FFFF | 4K                    | Reserved          |

| 0xFF000000-0xFF00EFFF | 60K                   | Reserved          |

| 0xFE000000-0xFEFFFFFF | 16M                   | CS_STM            |

| 0xFDF31000–0xFDFFFFFF | 828K                  | Reserved          |

| 0xFDF30000–0xFDF30FFF | 4K                    | PERI_DMAC         |

| 0xFDF20000–0xFDF2FFFF | 64K                   | Reserved          |

| 0xFDF18000–0xFDF1FFFF | 32K                   | Reserved          |

| 0xFDF14000–0xFDF17FFF | 16K                   | Reserved          |

| 0xFDF12000–0xFDF13FFF | 8K                    | Reserved          |

| 0xFDF11000–0xFDF11FFF | 4K                    | Reserved          |

| 0xFDF10000–0xFDF10FFF | 4K                    | PERF_STAT         |

| 0xFDF0F000–0xFDF0FFFF | 4K                    | Reserved          |

| 0xFDF0E000-0xFDF0EFFF | 4K                    | Reserved          |

| 0xFDF0D000–0xFDF0DFFF | 4K                    | 12C4              |

| 0xFDF0C000–0xFDF0CFFF | 4K                    | I2C3              |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xFDF0B000–0xFDF0BFFF | 4K                    | 12C7              |

| 0xFDF09000–0xFDF0AFFF | 8K                    | Reserved          |

| 0xFDF08000–0xFDF08FFF | 4K                    | SPI1              |

| 0xFDF07000–0xFDF07FFF | 4K                    | Reserved          |

| 0xFDF06000–0xFDF06FFF | 4K                    | SPI4              |

| 0xFDF05000–0xFDF05FFF | 4K                    | UART5             |

| 0xFDF04000–0xFDF04FFF | 4K                    | Reserved          |

| 0xFDF03000–0xFDF03FFF | 4K                    | UART2             |

| 0xFDF02000–0xFDF02FFF | 4K                    | UART0             |

| 0xFDF01000–0xFDF01FFF | 4K                    | UART4             |

| 0xFDF00000–0xFDF00FFF | 4K                    | UART1             |

| 0xFC200000–0xFDEFFFFF | 29M                   | Reserved          |

| 0xFC186000–0xFC1FFFFF | 488K                  | Reserved          |

| 0xFC185000–0xFC185FFF | 4K                    | Reserved          |

| 0xFC184000–0xFC184FFF | 4K                    | Reserved          |

| 0xFC183000–0xFC183FFF | 4K                    | SDIO0             |

| 0xFC182000–0xFC182FFF | 4K                    | IOC MMC1          |

| 0xFC181000–0xFC181FFF | 4K                    | Reserved          |

| 0xFC180000–0xFC180FFF | 4K                    | PCIE0 APB CFG     |

| 0xFC100000–0xFC17FFFF | 512K                  | Reserved          |

| 0xFC080000–0xFC0FFFFF | 512K                  | Reserved          |

| 0xFC000000–0xFC07FFFF | 512K                  | PCIEPHY0          |

| 0xF8000000–0xFBFFFFFF | 64M                   | Reserved          |

| 0xF4000000-0xF7FFFFF  | 64M                   | PCIECtrl0         |

| 0xF3F00000–0xF3FFFFFF | 1024K                 | Reserved          |

| 0xF1300000-0xF3EFFFFF | 44M                   | Reserved          |

| 0xF12F0000–0xF12FFFFF | 64K                   | Reserved          |

| 0xF1110000–0xF12EFFFF | 1920K                 | Reserved          |

| 0xF110F000-0xF110FFFF | 4K                    | Reserved          |

| 0xF110E000-0xF110EFFF | 4K                    | Reserved          |

| 0xF110D000–0xF110DFFF | 4K                    | Reserved          |

| Address               | Space Capacity (byte) | Applicable Module       |

|-----------------------|-----------------------|-------------------------|

| 0xF110C000–0xF110CFFF | 4K                    | Reserved                |

| 0xF110B000–0xF110BFFF | 4K                    | Reserved                |

| 0xF110A000–0xF110AFFF | 4K                    | Reserved                |

| 0xF1109000–0xF1109FFF | 4K                    | Reserved                |

| 0xF1108000–0xF1108FFF | 4K                    | Reserved                |

| 0xF1104000–0xF1107FFF | 16K                   | Reserved                |

| 0xF1100000-0xF1103FFF | 16K                   | Reserved                |

| 0xF1000000-0xF10FFFFF | 1M                    | Reserved                |

| 0xF0E31000-0xF0FFFFFF | 1852K                 | Reserved                |

| 0xF0E30000-0xF0E30FFF | 4K                    | Reserved                |

| 0xF0E24000-0xF0E2FFFF | 48K                   | Reserved                |

| 0xF0E20000-0xF0E23FFF | 16K                   | Reserved                |

| 0xF0E00000-0xF0E1FFFF | 128K                  | Reserved                |

| 0xF0C00000–0xF0DFFFFF | 2M                    | Reserved                |

| 0xF0000000-0xF0BFFFFF | 12M                   | Reserved                |

| 0xED800000-0xEFFFFFFF | 40M                   | Reserved                |

| 0xEC000000–0xED7FFFFF | 24M                   | CSSYS_APB               |

| 0xEAC00000–0xEBFFFFFF | 20M                   | Reserved                |

| 0xEA980000-0xEABFFFFF | 2560K                 | Reserved                |

| 0xEA960000-0xEA97FFFF | 128K                  | Reserved                |

| 0xEA940000-0xEA95FFFF | 128K                  | Reserved                |

| 0xEA920000-0xEA93FFFF | 128K                  | Reserved                |

| 0xEA900000-0xEA91FFFF | 128K                  | Reserved                |

| 0xEA600000-0xEA8FFFFF | 3M                    | Reserved                |

| 0xEA400000-0xEA5FFFFF | 2M                    | Reserved                |

| 0xEA000000-0xEA3FFFFF | 4M                    | Reserved                |

| 0xE9900000-0xE9FFFFFF | 7M                    | Reserved                |

| 0xE98A0000-0xE98FFFFF | 384K                  | Reserved                |

| 0xE9890000-0xE989FFFF | 64K                   | MMC0_NOC_Service_Target |

| 0xE9880000-0xE988FFFF | 64K                   | MMC1_NOC_Service_Target |

| 0xE9870000-0xE987FFFF | 64K                   | AOBUS_Service_Target    |

| Address               | Space Capacity (byte) | Applicable Module      |

|-----------------------|-----------------------|------------------------|

| 0xE9860000-0xE986FFFF | 64K                   | DMA_NOC_Service_Target |

| 0xE9850000-0xE985FFFF | 64K                   | Reserved               |

| 0xE9840000-0xE984FFFF | 64K                   | SYS_BUS_Service_Target |

| 0xE9830000-0xE983FFFF | 64K                   | ASP_Service_Target     |

| 0xE9820000-0xE982FFFF | 64K                   | Reserved               |

| 0xE9810000-0xE981FFFF | 64K                   | Reserved               |

| 0xE9800000-0xE980FFFF | 64K                   | CFGBUS_Service_Target  |

| 0xE8E00000-0xE97FFFFF | 10M                   | Reserved               |

| 0xE8DD0000-0xE8DFFFFF | 192K                  | Reserved               |

| 0xE8DC0000-0xE8DCFFFF | 64K                   | Reserved               |

| 0xE8D86000–0xE8DBFFFF | 232K                  | Reserved               |

| 0xE8D85000-0xE8D85FFF | 4K                    | Reserved               |

| 0xE8D84000–0xE8D84FFF | 4K                    | Reserved               |

| 0xE8D83000–0xE8D83FFF | 4K                    | Reserved               |

| 0xE8D82000–0xE8D82FFF | 4K                    | Reserved               |

| 0xE8D81000–0xE8D81FFF | 4K                    | Reserved               |

| 0xE8D80000-0xE8D80FFF | 4K                    | Reserved               |

| 0xE8D08000–0xE8D7FFFF | 480K                  | Reserved               |

| 0xE8D00000-0xE8D07FFF | 32K                   | Reserved               |

| 0xE8CB0000-0xE8CFFFFF | 320K                  | Reserved               |

| 0xE8C80000-0xE8CAFFFF | 192K                  | Reserved               |

| 0xE8C30000-0xE8C7FFFF | 320K                  | Reserved               |

| 0xE8C00000-0xE8C2FFFF | 192K                  | Reserved               |

| 0xE8B00000–0xE8BFFFFF | 1M                    | Reserved               |

| 0xE8A24000–0xE8AFFFFF | 880K                  | Reserved               |

| 0xE8A23000–0xE8A23FFF | 4K                    | Reserved               |

| 0xE8A22000–0xE8A22FFF | 4K                    | Reserved               |

| 0xE8A21000-0xE8A21FFF | 4K                    | Reserved               |

| 0xE8A20000-0xE8A20FFF | 4K                    | GPIO21                 |

| 0xE8A1F000-0xE8A1FFFF | 4K                    | GPIO20                 |

| 0xE8A1E000-0xE8A1EFFF | 4K                    | Reserved               |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE8A1D000–0xE8A1DFFF | 4K                    | Reserved          |

| 0xE8A1C000–0xE8A1CFFF | 4K                    | GPIO17            |

| 0xE8A1B000–0xE8A1BFFF | 4K                    | GPIO16            |

| 0xE8A1A000–0xE8A1AFFF | 4K                    | GPIO15            |

| 0xE8A19000-0xE8A19FFF | 4K                    | GPIO14            |

| 0xE8A18000-0xE8A18FFF | 4K                    | GPIO13            |

| 0xE8A17000-0xE8A17FFF | 4K                    | GPIO12            |

| 0xE8A16000-0xE8A16FFF | 4K                    | GPIO11            |

| 0xE8A15000-0xE8A15FFF | 4K                    | GPIO10            |

| 0xE8A14000-0xE8A14FFF | 4K                    | GPIO9             |

| 0xE8A13000-0xE8A13FFF | 4K                    | GPIO8             |

| 0xE8A12000-0xE8A12FFF | 4K                    | GPIO7             |

| 0xE8A11000-0xE8A11FFF | 4K                    | GPIO6             |

| 0xE8A10000-0xE8A10FFF | 4K                    | GPIO5             |

| 0xE8A0F000-0xE8A0FFFF | 4K                    | GPIO4             |

| 0xE8A0E000-0xE8A0EFFF | 4K                    | GPIO3             |

| 0xE8A0D000–0xE8A0DFFF | 4K                    | GPIO2             |

| 0xE8A0C000–0xE8A0CFFF | 4K                    | GPIO1             |

| 0xE8A0B000–0xE8A0BFFF | 4K                    | GPIO0             |

| 0xE8A0A000–0xE8A0AFFF | 4K                    | Reserved          |

| 0xE8A09000-0xE8A09FFF | 4K                    | PCTRL             |

| 0xE8A08000–0xE8A08FFF | 4K                    | Reserved          |

| 0xE8A07000-0xE8A07FFF | 4K                    | WD1               |

| 0xE8A06000-0xE8A06FFF | 4K                    | WD0               |

| 0xE8A05000-0xE8A05FFF | 4K                    | Reserved          |

| 0xE8A04000-0xE8A04FFF | 4K                    | PWM               |

| 0xE8A03000-0xE8A03FFF | 4K                    | TIMER12           |

| 0xE8A02000-0xE8A02FFF | 4K                    | TIMER11           |

| 0xE8A01000-0xE8A01FFF | 4K                    | TIMER10           |

| 0xE8A00000-0xE8A00FFF | 4K                    | TIMER9            |

| 0xE8970000-0xE89FFFFF | 576K                  | Reserved          |

| Address               | Space Capacity (byte) | Applicable Module                |

|-----------------------|-----------------------|----------------------------------|

| 0xE896D000-0xE896FFFF | 12K                   | Reserved                         |

| 0xE896C000-0xE896CFFF | 4K                    | IOC                              |

| 0xE896B000-0xE896BFFF | 4K                    | IPC_NS                           |

| 0xE896A000-0xE896AFFF | 4K                    | Reserved                         |

| 0xE8960000-0xE8969FFF | 40K                   | Reserved                         |

| 0xE8950000–0xE895FFFF | 64K                   | Reserved                         |

| 0xE8940000–0xE894FFFF | 64K                   | NOC_VENC_Service_Target          |

| 0xE8930000-0xE893FFFF | 64K                   | NOC_VDEC_Service_Target          |

| 0xE8920000-0xE892FFFF | 64K                   | NOC_VCODECBUS_Service<br>_Target |

| 0xE8901000–0xE891FFFF | 124K                  | Reserved                         |

| 0xE8900000-0xE8900FFF | 4K                    | MEDIA2_CRG                       |

| 0xE88C0000-0xE88FFFFF | 256K                  | Reserved                         |

| 0xE8880000-0xE88BFFFF | 256K                  | VENC                             |

| 0xE8840000-0xE887FFFF | 256K                  | Reserved                         |

| 0xE8800000-0xE883FFFF | 256K                  | VDEC                             |

| 0xE87FF000–0xE87FFFFF | 4K                    | MEDIA1_CRG                       |

| 0xE87A0000–0xE87FEFFF | 380K                  | Reserved                         |

| 0xE8700000-0xE879FFFF | 640K                  | MEDIA_COMMON                     |

| 0xE86F0000-0xE86FFFFF | 64K                   | Reserved                         |

| 0xE86E0000-0xE86EFFFF | 64K                   | Reserved                         |

| 0xE86D0000-0xE86DFFFF | 64K                   | Reserved                         |

| 0xE86C0000-0xE86CFFFF | 64K                   | Reserved                         |

| 0xE86A0000–0xE86BFFFF | 128K                  | Reserved                         |

| 0xE8690000-0xE869FFFF | 64K                   | Reserved                         |

| 0xE8680000-0xE868FFFF | 64K                   | DBCU0_SMMU                       |

| 0xE867F000-0xE867FFFF | 4K                    | Reserved                         |

| 0xE867E000-0xE867EFFF | 4K                    | LDI1                             |

| 0xE867DC00–0xE867DFFF | 1K                    | DSC                              |

| 0xE867D800-0xE867DBFF | 1K                    | IFBC                             |

| 0xE867D400–0xE867D7FF | 1K                    | Reserved                         |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE867D000–0xE867D3FF | 1K                    | LDI0              |

| 0xE867C000–0xE867CFFF | 4K                    | DPP_SBL           |

| 0xE8670000-0xE867BFFF | 48K                   | DPP               |

| 0xE866F000-0xE866FFFF | 4K                    | DPE               |

| 0xE866E000-0xE866EFFF | 4K                    | DBUF1             |

| 0xE866D000-0xE866DFFF | 4K                    | DBUF0             |

| 0xE8661000–0xE866CFFF | 48K                   | Reserved          |

| 0xE8660C00–0xE8660FFF | 1K                    | Reserved          |

| 0xE8660800-0xE8660BFF | 1K                    | Reserved          |

| 0xE8660400–0xE86607FF | 1K                    | Reserved          |

| 0xE8660000-0xE86603FF | 1K                    | Reserved          |

| 0xE865C000-0xE865FFFF | 16K                   | Reserved          |

| 0xE865B000-0xE865BFFF | 4K                    | Reserved          |

| 0xE865A000–0xE865AFFF | 4K                    | Reserved          |

| 0xE8654000–0xE8659FFF | 24K                   | Reserved          |

| 0xE8653000-0xE8653FFF | 4K                    | Reserved          |

| 0xE8652000–0xE8652FFF | 4K                    | Reserved          |

| 0xE8651000–0xE8651FFF | 4K                    | Reserved          |

| 0xE8650000-0xE8650FFF | 4K                    | Reserved          |

| 0xE8648000–0xE864FFFF | 32K                   | Reserved          |

| 0xE8640000–0xE8647FFF | 32K                   | Reserved          |

| 0xE8638000–0xE863FFFF | 32K                   | Reserved          |

| 0xE8630000-0xE8637FFF | 32K                   | Reserved          |

| 0xE8628000–0xE862FFFF | 32K                   | Reserved          |

| 0xE8620000-0xE8627FFF | 32K                   | Reserved          |

| 0xE8613000–0xE861FFFF | 52K                   | Reserved          |

| 0xE8612000–0xE8612FFF | 4K                    | Reserved          |

| 0xE8611000–0xE8611FFF | 4K                    | DBUG              |

| 0xE8610800–0xE8610FFF | 2K                    | Reserved          |

| 0xE8610000–0xE86107FF | 2K                    | Reserved          |

| 0xE860B000-0xE860FFFF | 20K                   | Reserved          |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE860A000-0xE860AFFF | 4K                    | Reserved          |

| 0xE8609000-0xE8609FFF | 4K                    | Reserved          |

| 0xE8608000-0xE8608FFF | 4K                    | Reserved          |

| 0xE8607000-0xE8607FFF | 4K                    | Reserved          |

| 0xE8603400-0xE8606FFF | 15K                   | Reserved          |

| 0xE8602000-0xE86033FF | 5K                    | Reserved          |

| 0xE8601C00-0xE8601FFF | 1K                    | Reserved          |

| 0xE8601800-0xE8601BFF | 1K                    | Reserved          |

| 0xE8601600-0xE86017FF | 0.5K                  | Reserved          |

| 0xE8601400–0xE86015FF | 0.5K                  | DSI1              |

| 0xE8601200-0xE86013FF | 0.5K                  | Reserved          |

| 0xE8601000–0xE86011FF | 0.5K                  | DSI0              |

| 0xE8600000-0xE8600FFF | 4K                    | MMBUF_CFG         |

| 0xE85E0000–0xE85FFFFF | 128K                  | Reserved          |

| 0xE85D0000–0xE85DFFFF | 64K                   | Reserved          |

| 0xE85C0000–0xE85CFFFF | 64K                   | Reserved          |

| 0xE85B0000–0xE85BFFFF | 64K                   | SMMUv500_CFG      |

| 0xE8592000–0xE85AFFFF | 120K                  | Reserved          |

| 0xE8590000–0xE8591FFF | 8K                    | Reserved          |

| 0xE8584000–0xE858FFFF | 48K                   | Reserved          |

| 0xE8583000–0xE8583FFF | 4K                    | Reserved          |

| 0xE8582000–0xE8582FFF | 4K                    | Reserved          |

| 0xE8581000–0xE8581FFF | 4K                    | Reserved          |

| 0xE8580000-0xE8580FFF | 4K                    | Reserved          |

| 0xE8560000–0xE857FFFF | 128K                  | Reserved          |

| 0xE8520000–0xE855FFFF | 256K                  | Reserved          |

| 0xE8500000-0xE851FFFF | 128K                  | Reserved          |

| 0xE8400000–0xE84FFFFF | 1M                    | Reserved          |

| 0xE8380000-0xE83FFFFF | 512K                  | Reserved          |

| 0xE8360000-0xE837FFFF | 128K                  | Reserved          |

| 0xE8340000-0xE835FFFF | 128K                  | JPG_FD            |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE8320000–0xE833FFFF | 128K                  | JPG_SMMU          |

| 0xE8310000–0xE831FFFF | 64K                   | Reserved          |

| 0xE8305000-0xE830FFFF | 44K                   | Reserved          |

| 0xE8304000-0xE8304FFF | 4K                    | JPG_TOP           |

| 0xE8303000-0xE8303FFF | 4K                    | JPG_SMMU_MASTER   |

| 0xE8302000-0xE8302FFF | 4K                    | JPG_CVDR          |

| 0xE8301000–0xE8301FFF | 4K                    | JPG_DEC           |

| 0xE8300000-0xE8300FFF | 4K                    | JPG_ENC           |

| 0xE82D0000–0xE82FFFFF | 192K                  | Reserved          |

| 0xE82C0000–0xE82CFFFF | 64K                   | G3D               |

| 0xE82BA000–0xE82BFFFF | 24K                   | Reserved          |

| 0xE82B9000–0xE82B9FFF | 4K                    | CODEC_SSI         |

| 0xE82B8000–0xE82B8FFF | 4K                    | Reserved          |

| 0xE82B0000–0xE82B7FFF | 32K                   | GIC400            |

| 0xE8200000–0xE82AFFFF | 704K                  | Reserved          |

| 0xE8100000–0xE81FFFFF | 1M                    | CCI_CFG           |

| 0xE808C000–0xE80FFFFF | 464K                  | Reserved          |

| 0xE8080000–0xE808BFFF | 48K                   | DSP_ITCM          |

| 0xE8058000–0xE807FFFF | 160K                  | DSP_DTCM          |

| 0xE8054000–0xE8057FFF | 16K                   | Reserved          |

| 0xE8052000–0xE8053FFF | 8K                    | Reserved          |

| 0xE8050000–0xE8051FFF | 8K                    | Reserved          |

| 0xE804FC00–0xE804FFFF | 1K                    | DSD               |

| 0xE804F800-0xE804FBFF | 1K                    | SIO_BT            |

| 0xE804F400–0xE804F7FF | 1K                    | Reserved          |

| 0xE804F000–0xE804F3FF | 1K                    | SIO_AUDIO         |

| 0xE804EC00-0xE804EFFF | 1K                    | ASP_HDMI_SPDIF    |

| 0xE804E800-0xE804EBFF | 1K                    | ASP_HDMI_SIO      |

| 0xE804E400-0xE804E7FF | 1K                    | ASP_HDMI_ASP      |

| 0xE804E000-0xE804E3FF | 1K                    | ASP_CFG           |

| 0xE804D000-0xE804DFFF | 4K                    | ASP_WD            |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE804C000–0xE804CFFF | 4K                    | ASP_IPC           |

| 0xE804B000-0xE804BFFF | 4K                    | ASP DMAC          |

| 0xE804A000-0xE804AFFF | 4K                    | ASP_TIMER1        |

| 0xE8049000-0xE8049FFF | 4K                    | ASP_TIMER0        |

| 0xE8048000–0xE8048FFF | 4K                    | ASP GPIO          |

| 0xE8047000-0xE8047FFF | 4K                    | Reserved          |

| 0xE8040000-0xE8046FFF | 28K                   | Reserved          |

| 0xE8028000-0xE803FFFF | 96K                   | Reserved          |

| 0xE8000000-0xE8027FFF | 160K                  | Reserved          |

| 0xE7FC0000–0xE7FFFFF  | 256K                  | Reserved          |

| 0xE7F80000–0xE7FBFFFF | 256K                  | Reserved          |

| 0xE7F00000–0xE7F7FFFF | 512K                  | USB AUDIO         |

| 0xE4000000–0xE7EFFFFF | 63M                   | Reserved          |

| 0xE3C00000–0xE3FFFFFF | 4M                    | Reserved          |

| 0xE3A03000–0xE3BFFFFF | 2036K                 | Reserved          |

| 0xE3A02000–0xE3A02FFF | 4K                    | Reserved          |

| 0xE3A00000-0xE3A01FFF | 8K                    | Reserved          |

| 0xE39D8000–0xE39FFFFF | 160K                  | Reserved          |

| 0xE3940000-0xE39D7FFF | 608K                  | Reserved          |

| 0xE38D8000-0xE393FFFF | 416K                  | Reserved          |

| 0xE3840000-0xE38D7FFF | 608K                  | Reserved          |

| 0xE3800000-0xE383FFFF | 256K                  | Reserved          |

| 0xE36C0000–0xE37FFFFF | 1M1.25M               | Reserved          |

| 0xE3600000-0xE36BFFFF | 768K                  | Reserved          |

| 0xE3580000-0xE35FFFFF | 512K                  | Reserved          |

| 0xE3500000-0xE357FFFF | 512K                  | Reserved          |

| 0xE3480000-0xE34FFFFF | 512K                  | Reserved          |

| 0xE3400000-0xE347FFFF | 512K                  | Reserved          |

| 0xE3200000-0xE33FFFFF | 2M                    | Reserved          |

| 0xE3100000-0xE31FFFFF | 1M                    | Reserved          |

| 0xE3000000-0xE30FFFFF | 1M                    | Reserved          |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE2400000–0xE2FFFFFF | 12M                   | Reserved          |

| 0xE2000000-0xE23FFFFF | 4M                    | Reserved          |

| 0xE1000000–0xE1FFFFFF | 16M                   | Reserved          |

| 0xE0840000–0xE0FFFFFF | 7936K                 | Reserved          |

| 0xE0800000-0xE083FFFF | 256K                  | Reserved          |

| 0xE0780000-0xE07FFFFF | 512K                  | Reserved          |

| 0xE0764000-0xE077FFFF | 112K                  | Reserved          |

| 0xE0760000-0xE0763FFF | 16K                   | Reserved          |

| 0xE0748000-0xE075FFFF | 96K                   | Reserved          |

| 0xE0740000-0xE0747FFF | 32K                   | Reserved          |

| 0xE0724000-0xE073FFFF | 96K                   | Reserved          |

| 0xE0720000-0xE0723FFF | 32K                   | Reserved          |

| 0xE0708000-0xE071FFFF | 96K                   | Reserved          |

| 0xE0700000-0xE0707FFF | 32K                   | Reserved          |

| 0xE0524000–0xE06FFFFF | 1904K                 | Reserved          |

| 0xE0520000-0xE0523FFF | 16K                   | Reserved          |

| 0xE0510000-0xE051FFFF | 64K                   | Reserved          |

| 0xE0500000-0xE050FFFF | 64K                   | NOC_SERVICE       |

| 0xE045C000–0xE04FFFFF | 656K                  | Reserved          |

| 0xE0458000-0xE045BFFF | 16K                   | Reserved          |

| 0xE0457000-0xE0457FFF | 4K                    | Reserved          |

| 0xE0456000-0xE0456FFF | 4K                    | Reserved          |

| 0xE0455000-0xE0455FFF | 4K                    | Reserved          |

| 0xE0454000-0xE0454FFF | 4K                    | Reserved          |

| 0xE0453000-0xE0453FFF | 4K                    | Reserved          |

| 0xE0452000-0xE0452FFF | 4K                    | Reserved          |

| 0xE0445000-0xE0451FFF | 52K                   | Reserved          |

| 0xE0444000-0xE0444FFF | 4k                    | Reserved          |

| 0xE0443000-0xE0443FFF | 4k                    | Reserved          |

| 0xE0442000-0xE0442FFF | 4k                    | Reserved          |

| 0xE0441000-0xE0441FFF | 4K                    | Reserved          |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE0440000-0xE0440FFF | 4K                    | Reserved          |

| 0xE0400000-0xE043FFFF | 256K                  | Reserved          |

| 0xE0300000-0xE03FFFFF | 1024K                 | Reserved          |

| 0xE0224000-0xE02FFFFF | 880K                  | Reserved          |

| 0xE0223000-0xE0223FFF | 4K                    | Reserved          |

| 0xE0222000-0xE0222FFF | 4K                    | Reserved          |

| 0xE0220000-0xE0221FFF | 8K                    | Reserved          |

| 0xE0218000-0xE021FFFF | 32K                   | Reserved          |

| 0xE0217000-0xE0217FFF | 4K                    | Reserved          |

| 0xE0216000-0xE0216FFF | 4K                    | Reserved          |

| 0xE0215000-0xE0215FFF | 4K                    | Reserved          |

| 0xE0214000-0xE0214FFF | 4K                    | Reserved          |

| 0xE0213000-0xE0213FFF | 4K                    | Reserved          |

| 0xE0212000-0xE0212FFF | 4K                    | Reserved          |

| 0xE0211000-0xE0211FFF | 4K                    | Reserved          |

| 0xE0210000-0xE0210FFF | 4K                    | Reserved          |

| 0xE020F000-0xE020FFFF | 4K                    | Reserved          |

| 0xE020E000-0xE020EFFF | 4K                    | Reserved          |

| 0xE020D000-0xE020DFFF | 4K                    | Reserved          |

| 0xE020C000-0xE020CFFF | 4K                    | Reserved          |

| 0xE020B000-0xE020BFFF | 4K                    | Reserved          |

| 0xE020A000–0xE020AFFF | 4K                    | Reserved          |

| 0xE0209000-0xE0209FFF | 4K                    | Reserved          |

| 0xE0208000-0xE0208FFF | 4K                    | Reserved          |

| 0xE0207000–0xE0207FFF | 4K                    | Reserved          |

| 0xE0206000-0xE0206FFF | 4K                    | Reserved          |

| 0xE0205000-0xE0205FFF | 4K                    | Reserved          |

| 0xE0204000-0xE0204FFF | 4K                    | Reserved          |

| 0xE0203000-0xE0203FFF | 4K                    | Reserved          |

| 0xE0202000-0xE0202FFF | 4K                    | Reserved          |

| 0xE0201000-0xE0201FFF | 4K                    | Reserved          |

| Address               | Space Capacity (byte) | Applicable Module |

|-----------------------|-----------------------|-------------------|

| 0xE0200000-0xE0200FFF | 4K                    | Reserved          |

| 0xE0100000-0xE01FFFFF | 1M                    | Reserved          |

| 0xE0000000-0xE00FFFFF | 1M                    | Reserved          |

| 0x00000000-0xDFFFFFFF | 3584M                 | DRAM              |

# **3** Mobile Processing Module

## 3.1 CPU

#### 3.1.1 Overview

The main processor is a big.LITTLE heterogeneous CPU subsystem that consists of the Cortex-A73 MP and Cortex-A53 MP processors. The Cortex-A73 MP and Cortex-A53 MP processors are based on the ARMv8-A architecture.

The Cortex-A73 MP processor has the following features:

- Processing performance of 3.66 DMIPS/MHz

- Superscaler, variable-length, and out-or-order pipeline

- Dynamic branch prediction with the branch target buffer (BTB), global history buffer (GHB), return address stack, and indirect predictor

- Fully-associative L1 instruction translation lookaside buffer (TLB) with 32 entries, supporting the page entry size of 4 KB, 16 KB, 64 KB, or 1 MB

- Fully-associative L1 data TLB with 48 entries, supporting the page entry size of 4 KB, 16 KB, 64 KB, or 1 MB

- 4-channel set-associative L2 TLB with 1024 entries

- Fixed size of 64 KB for the L1 instruction cache and 64 KB for the L1 data cache

- 2 MB L2 cache shared by the data and instruction

- ACE bus interface

- VFP and NEON units

- ARMv8-based Cryptography extended instruction

- External GIC

- Internal 64-bit universal counter for each CPU

- Independent power-off for the CPU core

The Cortex-A53 MP processor has the following features:

- Processing performance of 2.3 DMIPS/MHz

- In-order pipeline, supporting dual-instruction execution

- Direct and indirect branch prediction

- Two independent fully-associative L1 TLBs (with each having 10 entries) for instructions and data read/write, respectively.

- 2-channel set-associative L2 TLB with 256 entries

- 32 KB L1 data cache and 32 KB L1 instruction cache

- 1MB L2 cache shared by the data and instruction

- ACE bus interface

- ETM trace debugging

- CTI multi-core debugging

- Performance statistics unit with the PMUv3 architecture

- VFP and NEON units

- ARMv8-based Cryptography extended instruction

- External GIC

- Internal 64-bit universal counter for each CPU

- Independent power-off for the CPU core

The Cortex-A73 MP and Cortex-A53 MP processors use the CCI-550 to implement consistency of cache data, GIC-400 for interrupt virtualization, system counter for timer virtualization, and event interface for event interaction.

#### 3.1.2 Operating Mode

#### **3.1.2.1** Operating States

The Cortex-A73 MP and Cortex-A53 MP processors have the following four operating states, which are determined by the ARMv8-A architecture:

- Architecture state: AArch32 or AArch64

- Instruction set state: determined by the supported instruction set. The instruction set states include A32, T32, and A64.

- Exception level state: There are four exception level states, as described in Table 3-1.

- Security state: non-secure state or secure state

#### **3.1.2.2 Exception Level**

Table 3-1 lists the ARMv8-A exception levels.

| Exception Level of the Processor | Description                                                                                                                |

|----------------------------------|----------------------------------------------------------------------------------------------------------------------------|

| EL0                              | Execution mode of the user program, non-privileged, one mode<br>for the Secure World and one mode for the Non-Secure World |

| EL1                              | Running mode of the operating system, privileged, one mode for<br>the Secure World and one mode for the Non-Secure World   |

| EL2                              | Mode used for virtualization extension, used only in the Non-Secure World                                                  |

| EL3                              | Mode used to switch between the Secure World and Non-Secure World                                                          |

## 3.2 GPU

#### 3.2.1 Overview

The GPU is used to process three-dimensional images and special effects. The key technologies include polygon conversion, illuminant processing, cubic environment material textures and vertex blending, texture compression, and bump mapping as well as rendering.

#### 3.2.2 Operating Mode

The GPU mainly processes the 3D graphics in the SoC system. It has the following features:

- Integrated with the latest ARM Heimdall MP12 GPU and configured with two 512 KB L2 caches, effectively saving bus bandwidth. Each core integrates three arithmetic logic units (ALUs) to provide powerful floating-point computing capabilities.

- Power-off in idle hours. Each module of the GPU has a multi-level clock gating structure, which effectively reduces the GPU standby power consumption.

- Dynamic voltage frequency switch (DVFS) and AVS policies to dynamically adjust or monitor the working voltage and frequency of the GPU, effectively reducing the GPU power consumption.

- 23 texture compression formats, as shown in Table 3-2.

| No. | Compression Format      |

|-----|-------------------------|

| 1   | AFBC                    |

| 2   | ETC2                    |

| 3   | EAC, 1 component        |

| 4   | ETC2 + EAC              |

| 5   | EAC, 2 components       |

| 6   | NXR                     |

| 7   | BC1_UNORM (DXT1)        |

| 8   | BC2_UNORM (DXT3)        |

| 9   | BC3_UNORM (DXT5)        |

| 10  | BC4_UNORM (RGTC1_UNORM) |

| 11  | BC4_SNORM (RGTC1_SNORM) |

| 12  | BC5_UNORM (RGTC2_UNORM) |

| 13  | BC5_SNORM (RGTC2_SNORM) |

| 14  | BC6H_UF16               |

| 15  | BC6H_SF16               |

| 16  | BC7_UNORM               |

**Table 3-2** Texture compression formats supported by the GPU

| No. | Compression Format         |

|-----|----------------------------|

| 17  | EAC_SNORM, 1 component     |

| 18  | EAC_SNORM, 2 components    |

| 19  | ETC2 + punch-through alpha |

| 20  | ASTC 3D LDR                |

| 21  | ASTC 3D HDR                |

| 22  | ASTC 2D LDR                |

| 23  | ASTC 2D HDR                |

#### 3.3 I/O Processor

The internal processor of the I/O processor (IOMCU) is Cortex-M7. It provides one AXI master interface (shared by Cortex-M7 and DMA), one AHB master interface, and two AHB slave interfaces for external communication. The processor also supports delivery of instructions through ETM trace and debug AHB interfaces for debugging.

In addition, the IOMCU has common peripheral intellectual properties (IPs), including:

- Two SPI modules

- Three UART interface modules

- One BLPWM interface module

- Four I<sup>2</sup>C interface modules

- One DMA module

- One 32 kHz clock timer and one high frequency clock timer (FTimer)

- One watch dog

- Four groups of GPIOs

- One RTC module

- One task coprocessor TCP module

## **4** Media Processing

#### 4.1 Overview

The Hi3670 integrates a powerful multimedia processing subsystem. This subsystem is used for applications such as picture capturing and processing, LCD control and display post processing, video encoding/decoding acceleration and image post processing, 2D/3D graphics acceleration, intelligent computing, and audio capturing/output processing.

## **4.2 VENC**

#### 4.2.1.1.1 Introduction

The Hi3670 integrates the H.264 and H.265 hardware video encoders (VENCs), which support the H.264 standard and H.265 standard, respectively.

The VENC has the following features:

- One H.264 encoder

- Tool for the H.264 baseline profile

- I-slice and P-slice

The 4 x 4 and 16 x 16 intra-frame division methods support the DC, V, and H prediction modes.

The 8 x 8 and 16 x 16 inter-frame division methods are supported.

The MB-level bit rate control is supported.

The inter-frame prediction is supported for the 1/2 and 1/4 pixels.

The cosine transform supports Hadamard transform.

- De-blocking is supported.

- New tool for the H.264 baseline profile

- The context-adaptive binary arithmetic coding (CABAC) is supported.

- New tool for the H.264 high profile

- Apart from the 4 x 4 transform, the 8 x 8 transform is also supported.

- The 8 x 8 intra-frame prediction is supported.

- Input data formats

planar YUV 4:2:0 planar YUV 4:2:2 semi-planar YUV 4:2:0 semi-planar YVU 4:2:0 package UYVY4:2:2, VYUY4:2:2 package YUYV4:2:2, YVYU4:2:2 ARGB/BGRA8888

- ABGR/RGBA8888

- Output data formats: raw streams in the preceding formats

- Maximum resolution: 3840×2160; 2-pixel horizontal/vertical step

- Maximum frame rate: 720p@240 fps

- Maximum bit rate: 80 Mbit/s

- Frame storage format: linear

- Minimum resolution: 176x144

- One H.265 encoder

- Tool for the H.265 main profile

- I-slice and P-slice

The 4 x 4, 8x 8, 16 x 16, and 32 x 32 intra-frame division methods are supported. The 4 x 4, 8x 8, and 16 x 16 division methods support 35 prediction modes. The 32 x 32 division supports the DC/Planar prediction mode.

The 8x 8, 16 x 16, 32 x 32, and 64 x 64 inter-frame division methods are supported.

The CU-level bit rate control is supported.

The  $\pm 512$  horizontal integer search and  $\pm 144$  vertical integer search are supported.

The inter-frame prediction is supported for the 1/2 and 1/4 pixels.

DCT4/8/16/32 and DST4 are supported.

Merge and MergeSkip are supported.

TMV is supported.

De-blocking and sample adaptive offset (SAO) are supported.

- Input data formats:

- planar YUV 4:2:0

- planar YUV 4:2:2

semi-planar YUV 4:2:0

semi-planar YVU 4:2:0

- package UYVY4:2:2, VYUY4:2:2

- package YUYV4:2:2, YVYU4:2:2

- ARGB/BGRA8888

- ABGR/RGBA8888

- Output data formats: raw streams in the preceding formats

- Maximum resolution: 3840×2160; 2-pixel horizontal/vertical step

- Maximum frame rate: 720p@240 fps

- Maximum bit rate: 60 Mbit/s

- Frame storage format: linear

- Minimum resolution: 176x144

#### 4.2.1.1.2 Functional Block Diagram

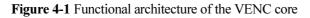

Figure 4-1 shows the architecture of the VENC core. The frames to be encoded are directly read to the sequencer through the busctrl, and the subsequent encoding is started. After the encoding is complete, the frames are output to the bus through the busctrl.

#### 4.2.1.1.3 Encoding Process

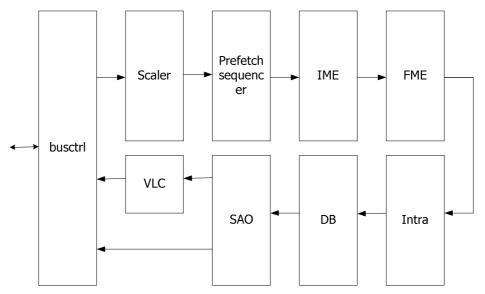

Figure 4-2 shows the encoding process of the VENC. After the encoding starts, the VENC performs parameter analysis and calculation. Then, it uses Colour Space Conversion to convert the color space of the input video source, searches for the integer motion vector in Integer motion estimation (IME), and then searches for the subpixel motion vector in Fraction motion estimation (FME). Finally, the reconstructed image is input to the DB/SAO, and the residual code stream input is put into the VLC for encoding.

#### Figure 4-2 VENC encoding workflow

# **4.3 VDEC**

# 4.3.1 Function Description

#### 4.3.1.1.1 Introduction

The Hi3670 integrates a VDEC that supports the VP9, H.265, H.264, MPEG1, MPEG2, MPEG4, VC1 (including WMV9), VP6, and VP8 protocols.

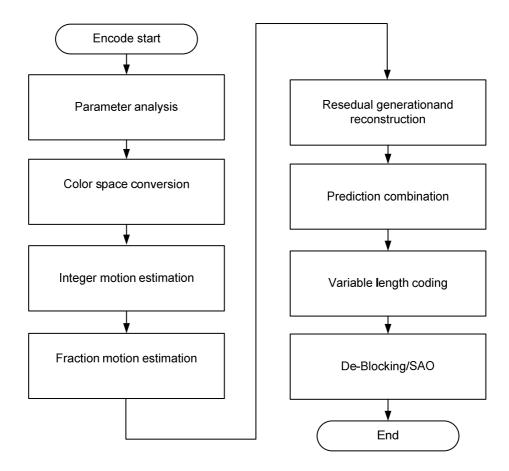

The VDEC consists of the video firmware (VFMW) running on the ARM processor and an embedded hardware video decoding engine. The VFMW obtains streams from the upper-layer software, parses the streams, and calls the video decoding engine to generate the image decoding sequences.

The sequences are under the control of the upper-layer software and output by the downstream module to a monitor or other devices. The VDEC has the following features:

- VP9 Profile2 (10 bits or less)

- Maximum video resolution: 4K x 2K (3840 x 2160)

- Maximum decoding rate: 100 Mbit/s or 4K x 2K@60 fps

- ITU-T H.265 Main Profile 10@Level 5.1 High-tier (and lower levels)

- Maximum video resolution: 4K x 2K (3840 x 2160)

- Maximum decoding rate: 160 Mbit/s or 4K x 2K@60 fps

- ITU-T H.264 High Profile@Level 5.0 (and lower levels)

- Maximum video resolution: 4K x 2K (3840 x 2160)

- Maximum decoding rate: 135 Mbit/s or 4K x 2K@30 fps

- ISO/IEC 13818-2 (MPEG2) Main Profile@high level and backward-compatible with MP@ML, MP@LL, SP@ML, and ISO/IEC 11172-2 (MPEG1)

- Maximum video resolution: 1080p (1920 x 1080)

- Maximum decoding rate: 80 Mbit/s or 60 fps

- ISO/IEC 14496-2 (MPEG4) Advanced Simple Profile@L0–5, compatible with the short header format and ISO/IEC 14496-2 Simple Profile@L0–3

- Maximum video resolution: 1080p (1920 x 1080)

- Maximum decoding rate: 50 Mbit/s or 60 fps

- VC1 SP@ML, MP@HL, and AP@L3

- Maximum video resolution: 1080p (1920 x 1080)

- Maximum decoding rate: 45 Mbit/s or 60 fps

- VP6

- Maximum video resolution: 1080p (1920 x 1080)

- Maximum decoding rate: 50 Mbit/s or 60 fps

- VP8

- Maximum video resolution: 1080p (1920 x 1080)

- Maximum decoding rate: 50 Mbit/s or 60 fps

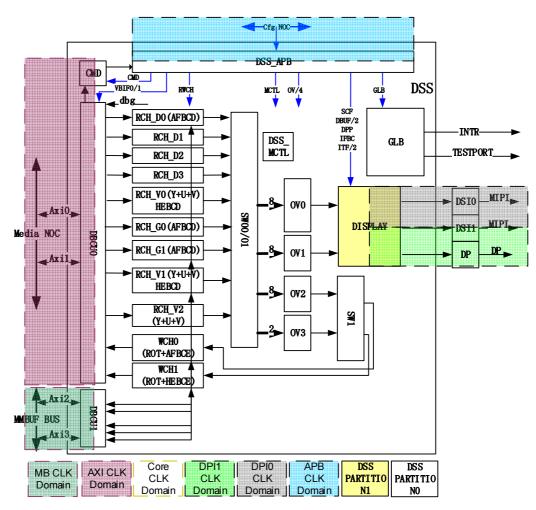

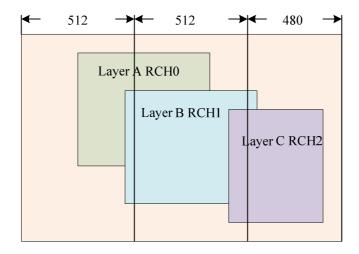

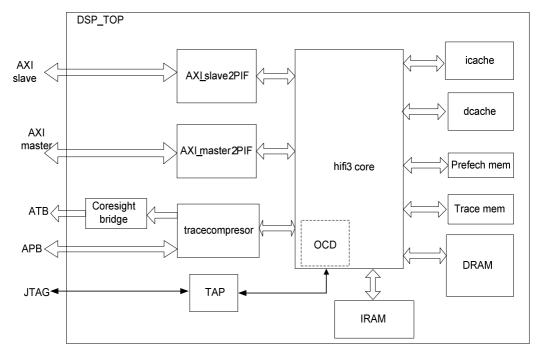

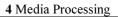

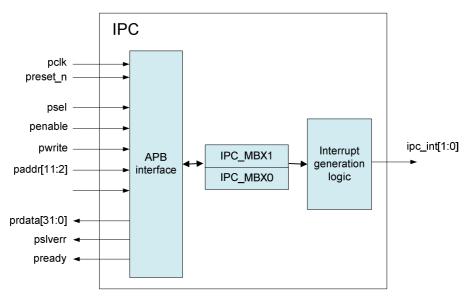

- Maximum decoding capability