Accelerating Your Ultra96 Developments

Learn how to use SDSoC to accelerate functions from the processors to the logic in the Ultra96!

Project Details

- Creator: Adam Taylor

- Project Name: Accelerating Your Ultra96 Developments

- Type of Project: Demonstrations (Projects showcasing individual features of a 96Boards product)

- Project Category: MPSoC, Hardware Acceleration

- Board(s) used: Ultra96

Introduction

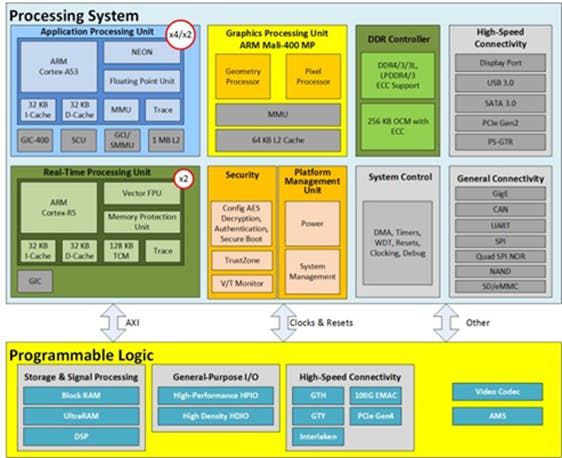

The Ultra96 provides both processors system and programmable logic. One of the key benefits of this heterogeneous approach is the ability to accelerate functions from the running on the processing system to being implemented in logic.

Done correctly (we will explore this more further down) moving functions into the programmable logic results in a significant acceleration in performance.

To get the best from this acceleration, we also want to accelerate the design cycle and remove the need to create separate PS / PL developments. These separate design processes have traditionally accounted for an increased development time when accelerating functions into the PL.

This increasing time scale stems from the need to create a hardware description language (HDL) block, verify its performance and create SW to drive the new module.

Ideally what we want is a system optimizing compiler which allows us to move functions between the PS and PL seamlessly and with ease.

Resources

RSS URL

Social Media Links

- Adam Taylor: Hackster.io

- 96Boards: URL | Twitter | Facebook | Linkedin